Circuits Intégrés : Travaux Dirigés MOS - GEC 2ème année

Telechargé par

lasmer marwen

Année Universitaire 2020-2021

1

2

ème

année GEC

Circuits Intégrés : Travaux Dirigés N° 1

Exercice 1

Soit un transistor MOS à canal N avec une tension de seuil V

T

= 2V et une polarisation

V

S

=0, V

D

= V

G

= 3V. Dans ces conditions, on mesure un courant de drain I

D

= 1mA.

Répondre aux questions suivantes en utilisant le modèle simplifié du MOS (sans effet de

substrat).

a) Le point de fonctionnement est-il dans la zone de conduction (non saturée) ou dans la

zone saturée des caractéristiques ?

b) Que devient le courant I

D

si la polarisation est portée à V

D

= 5 V et V

G

= 4 V ?

c) Quelle est la résistance du canal R

on

autour de V

DS

= 0 V lorsque V

G

= 4 V ?

Exercice 2

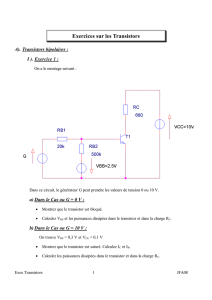

Soit le circuit suivant :

Caractéristiques du MOST : V

T

= 1 V, ß = 0.2 mA/V

a) Pour R =10 kΩ, calculer la tension V

out

pour les deux valeurs de la tension d’entrée V

in

= 0

V et V

in

= 5 V.

b) Déterminer la valeur minimum de R pour que V

out

soit inférieur à 1 V lorsque V

in

= 5 V.

Exercice 3

Soit le montage de la figure suivante utilisant un transistor MOS.

1/ Pour quelles valeurs de U

1

le transistor ne conduit-il pas ?

2/ Quelle est la condition sur U

2

pour que le MOS soit en saturation ?

Année Universitaire 2020-2021

2

3/ Déterminer dans un plan (U

1

; U

2

) les différentes zones de fonctionnement du transistor.

4/ Calculer dans chaque zone, la tension U

2

= f(U

1

) et la représenter sur un diagramme en

fonction de U

1

.

Application numérique : V

T

= 0.5 V R

1

=10 kW

K = 50 mA/V

2

V

cc

= 4.5 V

Exercice 4

On donne :

La tension de seuil V

t

=1V

Le paramètre de transconductance K

n

=10mA/V

2

La tension V

D

=8.4V

1. Déterminer les coordonnés de point de repos (V

GS

, I

D

, V

DS

)

2. Calculer les paramètres « petit signal » (transconductance g

m

et résistance de sortie

r

o

)

3. Donnez le schéma équivalent en alternatif.

En déduire le gain en tension sans charge

En déduire le gain en tension avec charge

Déterminez les impédances d'entrée et de sortie du montage.

4. Reprendre la question 3 tout en éliminant la capacité Cs

Exercice 5

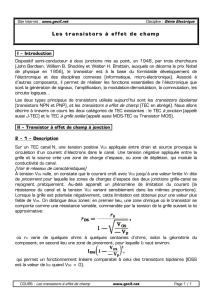

Soit le montage ci-dessous

:

Année Universitaire 2020-2021

3

1. Donnez la nature du transistor

2. Déterminez les coordonnées du point de repos, on donne : V

p

=-5V ; C

1

=0,33µF ;

I

DSS

=6mA ; C

2

=1µF ; R

G

=20Méga ohm V

DD

=15V ; R

D

=R

L

=1K ; R

i

=10K

3. Calculez la valeur de la transconductance g

m

au point Q (point de repos)

4. Donnez le schéma équivalent en alternatif.

En déduire le gain en tension v

0

/v

i

et A

0

=v

0

/v

gs

Déterminez les impédances d'entrée et de sortie du montage.

Déterminez l'expression de v

0

lorsque v

i

=10sin(377t) (mv)

5. Calculez les fréquences de coupure haute et basse de cet amplificateur sachant que

C

gs

=5pF; C

gd

=2pF; C

ds

=1pF. En déduire la bande passante.

Exercice 6

Soit la cellule CMOS donnée ci-dessous.

Données concepteur :

· Largeur des transistors M1 et M2 : W1=W2=100mm ;

· Tous les transistors sont à la longueur minimale L=Lmin=10mm ;

· VDD=5V.

Paramètres fondeur :

Année Universitaire 2020-2021

4

· NMOS : VTO=1V ; KP=20e

-6

; LAMBDA=0.01 ; TOX=200e

-10

; CGDO=200e

-12

;

CGSO=200e

-12

· PMOS : VTO=-1V ; KP=10e

-6

; LAMBDA =0.01 ; TOX=200e

-10

; CGDO=200e

-12

;

CGSO=200e

-12

1 / Polarisation

a) Dimensionnez les transistors M

3

et M

4

de façon à polariser le point A à 3V.

Aide à la résolution : M

3

et M

4

ne servent qu'à assurer la polarisation de la grille de M

2

à la

valeur souhaitée. Pour déterminer le rapport des largeurs W

3

/W

4

des transistors, il faut égaler

les expressions des courants des deux transistors. La relation liant V

DD

et les V

GS

des

transistors donne une seconde équation qui, combinée à la première, permet de trouvez la

valeur du rapport W

3

/W

4

. Sachant que la plus petite dimension possible pour un W est

donnée par la dimension L

min

du fondeur et sachant que l'on cherche à minimiser la surface

de silicium, on en déduit les valeurs numériques de W

3

et W

4

.

b) Calculez les courants qui parcourent tous les transistors du montage.

c) Calculez la tension continue à appliquer sur la grille de M

1

pour positionner la sortie V

o

à

V

DD

/2, en régime continu.

d) Calculez les paramètres g

m

et g

o

des quatre transistors.

2 / Régime dynamique

a) Donnez le schéma équivalent basses fréquences de la cellule.

Aide à la résolution : en régime dynamique, seuls les transistors de la cellule amplificatrice

doivent être modélisés.

b) Calculez les impédances d'entrée et de sortie du montage Rin et R

out

de cette cellule.

Calculez son gain en tension A

V

=v

o

/v

i

.

3 / Etude en fréquence

a) Calculez la valeur des capacités parasites qui interviennent dans le modèle en fréquence

des transistors.

Aide à la résolution : le calcul se fait à partir des données fondeurs et des dimensions des

transistors (cellule de base seulement)

b) Donnez le schéma dynamique en fréquence (avec prise en compte des capacités

parasites des transistors) en prenant en compte l'existence d'une source de tension petit

signal v

s

d'impédance R

s

=100kΩ connectée sur l'entrée du montage.

c) Retrouver les expressions du cours pour les fréquences des pôles f

1

, f

2

et du zéro f

z

.

d) A partir de ces expressions (non simplifiées) calculez la fréquence des pôles et du zéro.

1

/

4

100%