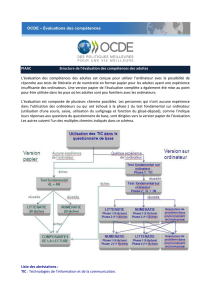

Direction Générale des Etudes

Technologiques

---*---

Institut Supérieur des Etudes

Technologiques de

Mahdia

Arch

i

t

ec

t

ure Des

O

r

d

i

na

t

eurs

T

echno

l

o

g

i

es e

t

conce

p

t

s

…

A

nn

ée

U

n

iv

e

r

s

itai

r

e

2009-2010

i

T

a

bl

e

d

es

m

a

t

i

è

r

es

CHAPITRE I :

HISTORIQUE ET INTRODUCTION A L’INFORMATIQUE....................................................................... 3

1. INTRODUCTION ............................................................................................................................................... 4

2. CONCEPTS ET DEFINITIONS ............................................................................................................................. 4

3. HISTORIQUE DES ORDINATEURS...................................................................................................................... 6

4. ORGANISATION ET FONCTIONNEMENT D’UN ORDINATEUR.............................................................................. 8

4.2. STRUCTURE D’UN ORDINATEUR ................................................................................................................. 10

CHAPITRE II :

REPRESENTATION DE L’INFORMATION................................................................................................. 12

1. INTRODUCTION ............................................................................................................................................. 12

2. REPRESENTATION DES INSTRUCTIONS........................................................................................................... 13

3. DONNEES NON NUMERIQUES......................................................................................................................... 14

4. DONNEES NUMERIQUES : .............................................................................................................................. 14

5. RECAPITULATIF DES DIFFERENTES REPRESENTATIONS RELATIVES AUX DONNEES : ...................................... 30

CHAPITRE III :

LA MEMOIRE CENTRALE............................................................................................................................. 37

1. INTRODUCTION ............................................................................................................................................. 38

2. LE FONCTIONNEMENT DE LA MEMOIRE CENTRALE........................................................................................ 38

3. ORGANISATION INTERNE DE LA MEMOIRE CENTRALE ................................................................................... 41

4. CARACTERISTIQUES DE LA MEMOIRE CENTRALE........................................................................................... 42

5. HIERARCHIE DE LA MEMOIRE CENTRALE ...................................................................................................... 43

6. ASSEMBLAGE DE BLOCS MEMOIRES POUR CONSTITUER LA MEMOIRE CENTRALE .......................................... 43

CHAPITRE IV :

UNITE CENTRALE DE TRAITEMENT ........................................................................................................ 48

1. INTRODUCTION ............................................................................................................................................. 48

2. JEU D’INSTRUCTIONS .................................................................................................................................... 49

3. REGISTRES DE LA CPU : ............................................................................................................................... 49

4. UNITE DE COMMANDE................................................................................................................................... 51

5. UNITE ARITHMETIQUE ET LOGIQUE ............................................................................................................... 52

6. CYCLE INSTRUCTION..................................................................................................................................... 53

7. EXEMPLE DE JEU D’INSTRUCTIONS A UNE ADRESSE ...................................................................................... 56

CHAPITRE V :

LES ENTREES/SORTIES ................................................................................................................................. 60

1. INTRODUCTION ............................................................................................................................................. 60

2. LES BUS ET LEUR FONCTIONNEMENT............................................................................................................. 61

3. LES CONTROLEURS D’E /S ............................................................................................................................ 66

4. ARCHITECTURE ET PROCEDURES D’ECHANGE ............................................................................................... 68

A

r

chitectu

r

e et

m

aintenance de

s

o

r

dinateu

rs

I

SE

T

M

ahdia

C

h

a

pi

t

r

e

I

:

H

i

s

t

o

r

iqu

e

e

t

in

t

r

odu

c

t

ion

à

l’in

f

o

r

m

a

t

iqu

e

Obj

ec

t

i

f

s

du

c

h

a

pi

t

r

e

:

1

.

C

o

m

p

r

end

r

e

l

e

s c

on

c

ep

ts

de

ba

s

e

de

l’i

n

f

o

r

m

a

t

i

que

.

2

. S

e

f

a

m

ili

a

r

i

s

e

z

a

v

e

c

l

a

t

e

r

m

i

no

l

og

i

e

de

l’

a

r

c

h

i

t

e

ct

u

r

e

de

s

o

r

d

i

na

t

eu

r

s.

3

.

C

onna

ît

r

e

l

e

s

d

i

ff

é

r

en

t

e

s

géné

r

a

t

i

on

s

de

s

o

r

d

i

na

t

eu

r

s.

4

. S

’i

n

i

t

i

e

r

a

v

e

c

l

e

s

p

r

i

n

c

i

pe

s

de

ba

s

e

de

f

on

ct

i

onne

m

en

t

d

’

un

o

r

d

i

na

t

eu

r

.

M

o

t

s

c

l

és

du

c

h

a

pi

t

r

e

:

I

n

f

o

r

m

a

t

i

que

, T

r

a

i

t

e

m

en

t, I

n

f

o

r

m

a

t

i

on

,

D

onnée

,

O

r

d

i

na

t

eu

r

, I

n

st

r

u

ct

i

on

, P

r

og

r

a

mm

e

,

M

a

t

é

r

i

e

l

,

L

og

i

c

i

e

l

, Syst

è

m

e

i

n

f

o

r

m

a

t

i

que

,

C

a

l

c

u

l

a

t

eu

r

, T

ube

à

v

i

de

, T

r

an

s

i

st

o

r

,

C

i

r

c

u

i

t

i

n

t

ég

r

é

,

M

i

c

r

op

r

o

c

e

ss

eu

r

,

C

on

f

i

gu

r

a

t

i

on

,

U

n

i

t

é

c

en

t

r

a

l

e

, P

é

r

i

phé

r

i

que

,

E

n

t

r

ée

s/S

o

r

t

i

e

s,

M

é

m

o

i

r

e

c

en

t

r

a

l

e

,

U

n

i

t

é

c

en

t

r

a

l

e

de

t

r

a

i

t

e

m

en

t,

M

odè

l

e

de

V

on

N

eu

m

ann

,

U

n

i

t

é

de

c

o

mm

ande

,

U

n

i

t

é

a

r

i

t

h

m

é

t

i

que

e

t

l

og

i

que

.

El

é

m

e

n

t

s

d

e

c

on

t

e

nu

:

1. INTRODUCTION

2. CONCEPTS ET DEFINITIONS

3. HISTORIQUE DES ORDINATEURS

3.1.

L

a géné

r

ation

z

é

r

o

(

1642

-

1945

)

3.2.

L

a p

r

e

m

iè

r

e géné

r

ation

(

1945

-

1955

)

3.3.

L

a deuxiè

m

e géné

r

ation

(

1955

-

1965

)

3.4.

L

a t

r

oi

s

iè

m

e géné

r

ation

(

1965

-

1980

)

:

3.5.

L

a quat

r

iè

m

e géné

r

ation

(

à pa

r

ti

r

de 1980

)

:

4. CONFIGURATION ET STRUCTURE D’UN ORDINATEUR

4.1. Configu

r

ation

4.2. St

r

uctu

r

e d

’

un o

r

dinateu

r

4.3. P

r

incipe de fonctionne

m

ent d

’

un o

r

dinateu

r

Volu

m

e

ho

r

a

i

r

e

t

o

t

a

l

:

6

h

e

u

r

es

Ti

m

ing

a

pp

r

o

x

i

m

a

t

i

f

:

§

1

e

t

2

:

1

,

5

h

e

u

r

es

§

3

:

3

h

e

u

r

es

§

4

:

1

,

5

h

e

u

r

e

Page 3

A

r

chitectu

r

e et

m

aintenance de

s

o

r

dinateu

rs

I

SE

T

M

ahdia

1

. In

t

r

odu

c

t

ion

L’Homme a toujours eu besoin de compter. Au cours de la préhistoire, il ne savait

calculer qu’a l’aide de cailloux (en latin : calculi) ou de ses mains qui furent sans

doute, les premières calculatrices de poches. On trouve des traces de symboles et de

chiffres dans certaines civilisations de l’antiquité. Chinois, égyptiens, sumériens,

babyloniens, grecs ou romains, tous avaient des symboles numériques et des méthodes

pour compter et calculer.

Ces systèmes de numération s’inspiraient naturellement du nombre de doigts, des

mains et des pieds et des articulations correspondantes d’où on trouve les bases 10, 12,

14, 15, 24, 30, 60…etc. La plus naturelle et la plus répandue des numérations était

celle qui comptait en base 10 et elle nous est parvenue au cours des siècles.

Parallèlement à cette évolution des symboles, chiffres, calculs mentaux et manuels, on

assistait au développement d’outils, de systèmes, de machines pour simplifier et

accélérer les calculs nécessaires.

2

.

C

on

ce

p

t

s

e

t

d

é

f

ini

t

ion

s

A

r

c

h

itect

u

r

e d

’

un

o

r

di

n

ate

u

r

:

C’est la description de ses unités fonctionnelles ainsi que leur interconnexion et

coopération pour réaliser son fonctionnement global.

I

n

f

o

r

matiq

u

e

:

Terme employé pour la première fois en 1962 et provenant de la contraction de mots

« information » et « automatique ». Il a connu rapidement un grand succès et a été

adopté définitivement, dès 1966. L’académie française publia en 1965 la définition

suivante de l’informatique « la science du traitement rationnel de l’information,

considérée comme le support de connaissances dans les domaines scientifiques,

économiques et sociaux, notamment à l’aide de machines automatiques ».

I

n

f

o

r

matio

n

et do

nn

ée

:

Une donnée est un ensemble de chiffres et de lettres (symboles) qui n’a ni un sens ni

une interprétation précise. Une information est un ensemble de données qui a un sens

précis.

Figure 1 : Exemple de données et d’information

Année Taux de natalité

1980 5%

Sens

Données

Information

Page 4

A

r

chitectu

r

e et

m

aintenance de

s

o

r

dinateu

rs

I

SE

T

M

ahdia

O

r

di

n

ate

u

r

(

comp

u

te

r

)

:

Machine de traitement de l’information. Le terme anglais computer signifiait au départ

calculateur numérique électronique. Le terme français « ordinateur » est mieux adapté

car il s’éloigne de la connotation numérique. Un ordinateur est capable de

• Acquérir des informations ;

• Les sauvegarder d’une façon permanente ;

• Effectuer sur eux des traitements ;

• Les restituer.

I

n

s

t

r

u

ctio

n

et p

r

og

r

amme

:

Une instruction est une opération de base qu’un ordinateur est capable d’exécuter.

Exemple : l’addition de deux nombres.

N’importe quel traitement revient à exécuter une séquence d’instruction dans un ordre

précis. Par exemple le calcul de la moyenne de deux nombres.

Un programme est constitué de deux parties :

• Une partie contenant les données.

• Une partie code qui représente la séquence des instructions à exécuter.

Ha

r

dwa

r

e

(

M

até

r

iel

)

:

Ensemble de composantes matérielles constituant l’ordinateur.

S

o

f

twa

r

e

(

Logiciel

)

:

Ensemble de programmes (de taille importante) permettant de combler en terme de

traitement un besoin spécifique. Exemple le logiciel de traitement de texte « Microsoft

Word ». Il y a deux types de logiciels :

• Logiciel standard qui peut être utilisé par un grand nombre d’utilisateurs sans

qu’il soit modifié.

• Logiciel spécifique qui correspond aux besoins particuliers de certains

utilisateurs.

S

y

s

tème i

n

f

o

r

matiq

u

e

:

C’est l’ensemble de matériels et de logiciels nécessaires pour satisfaire les besoins

informatiques d’un ensemble d’utilisateurs.

S

y

s

tème d

’

exploitatio

n

:

Première couche logicielle permettant d'utiliser un ordinateur. Il supervise et

coordonne les différents modules qui le composent. Il joue le rôle d'interface

indispensable entre les différentes ressources matérielles et les applications logicielles.

Exemples : Linux, Windows, Mac Os, Unix, Etc.

Cycle de t

r

aiteme

n

t de l

’

i

n

f

o

r

matio

n

:

Pour tout type d’ordinateurs et pour tout type d’applications, le principe fondamental

de l’informatique repose sur un processus comportant généralement 3 phases :

• Entrée des données.

• Leur traitement et/ou leur sauvegarde.

• Sortie des résultats.

Page 5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

1

/

75

100%