27/04/2010 1 Cours 1 Microcontrôleur Plan du cours Pourquoi le

27/04/2010

1

1

Cours 1 Microcontrôleur

Jalil Boukhobza

LC 206

02 98 01 69 73

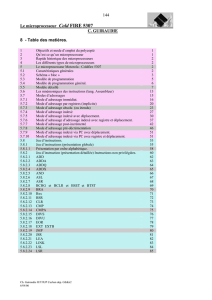

Plan du cours

1. Introduction

2. Signaux d’E/S et ports

3. L’unité centrale

4. Les modes d’adressage

5. Les instructions

2

Pourquoi le 68HC11 ?

Contient un microprocesseur de la même famille que celui

précédemment vu.

Peu cher

Très utilisé:

Lecteurs de code barres

Différents programmateurs

Robots

Thermostats d’ambiance

Contrôle d’affichage dans les voitures

…

2 modes de fonctionnement et 2 modes de Test

3

Source: http://www.arlabs.com/hc11chp.jpg

27/04/2010

2

Qu’est ce qu’un µcontrôleur

Un µcontrôleur intègre dans un même circuit:

Une unité centrale ou micro processeur (CPU)

De la mémoire (RAM, ROM, EPROM, EEPROM,...)

Des interfaces d'entrées/sorties

4

CPU mémoire

Périph

d’E/S

Entrée/sorties

µcontrôleur

Définition globale

Le 68HC11 est un µcontrôleur développé par Motorola

(devenu freescale) construit avec une unité centrale 8 bits.

Il contient:

un espace adressable (bus d'adresses de 16 bits).

Un convertisseur analogique/numérique 8 bits multiplexé sur 8 canaux.

Une interface de communication série asynchrone (RS232)

Une interface de communication série synchrone

Un timer 16 bits avec 3 entrées de capture et 4 sorties de comparaison

plus 1 E/S programmable

Plusieurs sources d'interruptions (internes et externes)

Plusieurs broches d'E/S polyvalentes réparties sur 5 ports.()

(DMA)

(Coprocesseur mathématique)

5

Structure globale

6

Source: « Microcontrôleur 68HC11 » C. Tavernier, Dunod 97

27/04/2010

3

68HC11 en bref

Mémoire subdivisée au max en 3 blocs:

RAM: mémoire vive d’au moins 256 octets et

toujours présente.

ROM: peut être présente ou absente mémoire

destinée aux programmes

ROM: programmable par masque lors de la fabrication

EPROM: programmable électriquement

OTPROM: non effaçable (One Time PROM)

EEPROM: effaçable plusieurs fois

EEPROM: destinée aux données

7

68HC11 en bref -2-

Unité centrale entourée d’un certain

nombre de ports parallèles:

Port A, B, C, D, E: bidirectionnels ou uni

directionnels

Certains ports sont partagés avec des ressources

internes et donc ne sont pas toujours accessibles: ex.

port E commun avec le convertisseur

Analogique/Digital

Entrées séries dispo:

SPI: Serial Peripheral Interface (synchrone)

SCI: Serial Communication Interface (asynchrone)

8

68HC11 en bref -3-

Ensemble de Timers disponible:

Plusieurs timers évolués

Accumulateur d’impulsions

Une horloge temps réel

Un chien de garde (COP Computer Operating Properly):

destiné à surveiller le fonctionnement du µcontrôleur

Convertisseur analogique digital à 8 entrées

2 modes de fonctionnement:

Mode « single chip »: fonctionne seul

Mode « expanded »: connecté à des circuits externes,

dans ce cas le port B et C se transforment en lignes

d’adresses et de données. 9

27/04/2010

4

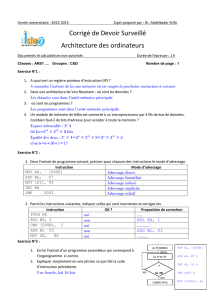

Famille du 68HC11

10

Source: « Microcontrôleur 68HC11 » C. Tavernier, Dunod 97

Famille du 68HC11 -2-

11

RAM

ROM

EPROM

EEPROM

TIMER

A/D

D/A

SCI,SPI

PWM

DMA

COPRO

PLL

PORTS

BROCHES

Famille A

256

0 à 8k

0

0 à 512

X

8 voies

1+1

A=>E

48,52

Famille D

192 à 256

0 à 4K

0

0

X

0 ou 4 voies

1+1

2

A=>H ou A=>D

64, 68 ou 40, 44

Famille M

1280

32K

0

640

8voies

1+2

4

X

X

A=>H ?

80 ?

….

Signaux d’E/S

Le 68HC11 est inclus dans un boitier a plusieurs broches. En plus des

E/S des ports, il possède plusieurs broches selon les versions:

VSS et VDD: alimentation VDD=5V, VSS=0.

XTAL et EXTAL: connexion d'un quartz ou d'une horloge externe.

E : sortie d'horloge.

IRQ et XIRQ: entrées d'interruptions externes.

VRH et VRL: tension de référence pour la conversion A/N.

VRH<VDD.

MODA et MODB: mode de fonctionnement.

RESET signal d'initialisation.

STRA et STRB: en mode normal (monopuce), signaux de

communication avec une interface parallèle.

12

27/04/2010

5

Structure globale

13

Source: « Microcontrôleur 68HC11 » C. Tavernier, Dunod 97

Port d’E/S

PA0-PA7: entrées: PA0-PA1-PA2 et

sorties PA3-PA4-PA5-PA6, et

entrée/sortie PA7. Lignes partagées

avec celles du Timer.

PB0-PB7: sorties parallèles en mode

«mono puce » et @ de poids forts en

mode étendu

PC0-PC7: E/S parallèles à usage

général en mode « mono puce » et

bits de poids faibles + données en

mode étendu. STRA indique si @ ou

données et STRB indique si lec/Ecr

PD0-PD5: E/S parallèle du port D,

communes avec les ports série (SPI

et SCI)

PE0-PE7: Entrées du port E partagée

avec les entrées du convertisseur

analogique/digital 14

Structure globale

15

Source: « Microcontrôleur 68HC11 » C. Tavernier, Dunod 97

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

1

/

16

100%