Article_ADIS_Innovation_VF-final-v3

Vers une filière et un support de conception EDA (Electronic

Design Automation) des fonctions de coupure spécifiques

Christophe Gineste1, Thierry Bouchet1, Olivier Gatti1, Jean-Christophe Crébier2, Patrick Austin3,4,

Nicolas Rouger2, Abdelhakim Bourennane3,4, Frédéric Morancho3,4 ,Marie Breil3,4

1 ADIS Innovation, 100 impasse des Houillères, ZI le Pontet 13590 Meyreuil

2 G2ELAB, ENSE3 bat D 11, rue des Mathématiques BP 46 38402 St Martin d'Hères Cedex

3 CNRS, LAAS, 7 avenue du colonel Roche, F-31400 Toulouse, France

4Univ de Toulouse, Université Paul Sabatier, LAAS, F-31400 Toulouse, France

Afin de répondre aux nouveaux défis de la gestion optimale de l’énergie électrique orientés vers les moyennes et hautes tensions, ADIS

Innovation développe une filière technologique d’intégration monolithique. Autour d’un cœur technologique qualifié et à l’aide d’outils de

conception EDA (Electronic Device Automation), ADIS est en mesure de fournir des produits industriels qualifiés intégrant des fonctions

de coupures et adaptées aux conditions de packaging et de mises en œuvre innovantes pour répondre au exigences en termes d‘intégration,

de fiabilité et de performance énergétique. D’abord validée sur silicium, cette filière sera ensuite déclinée sur les matériaux à large bande

interdite — grand gap — (SiC, GaN).

INTRODUCTION

La société ADIS Innovation a pour objectifs de répondre

aux besoins de conception et fabrication des composants de

puissance intégrés dédiés en s'appuyant sur un cœur

technologique propriétaire. Cette ambition doit permettre de

répondre aux nouveaux besoins croissants de la conversion

d’énergie orientée vers les moyennes et fortes puissances.

Ces composants intégrés sont conçus et fabriqués à partir

de trois éléments :

- un coeur technologique de puissance à structure

verticale type MOS/Bipolaire,

- un outil de conception type design kit permettant de

concevoir et d'intégrer la fonction de coupure incluant les

fonctionnalités rapprochées,

- un matériau support, le substrat, adapté au type et aux

caractéristiques souhaitées du composant de puissance.

I. LE CŒUR TECHNOLOGIQUE

Le cœur technologique d’ADIS Innovation est la brique

initiale, pierre angulaire des futurs composants développés.

Il s’agit de la cellule de puissance à structure verticale de

type MOS/Bipolaire autour de laquelle s’articuleront les

fonctions monolithiques. A ce cœur silicium sont associées

un ensemble d'étapes technologique favorisant l'intégration

fonctionnelle monolithique mais également la mise en

oeuvre et le packaging spécifique [11, 25]. La brique de

puissance MOS sera développée conjointement au procédé

de fabrication et optimisée de manière à positionner le cœur

technologique sur une large gamme de tensions (de

quelques centaines à quelques milliers de Volts) et courants

(quelques Ampères jusqu'à la centaine d’Ampères et au-

delà). Ce cœur technologique doit être robuste vis-à-vis des

divers cahiers des charges tout en offrant un support de

conception et d'intégration de fonctions monolithiques [1].

II. ETAT DE L’ART DE L’INTEGRATION

FONCTIONNELLE

Depuis vingt ans, par rapport aux systèmes discrets, les

développements autour de l’intégration monolithique

fonctionnelle en électronique de puissance ont montré de

forts apports tels que l’augmentation de la fiabilité et de la

performance, l'optimisation de la connectique, la

diminution du volume global et du poids, la réduction du

rayonnement et des couplages électromagnétiques du

système [2,3]. De son côté, l’intégration hybride, très

appliquée en électronique de puissance, consiste à

regrouper puis assembler tous les composants du système

dans un environnement commun [4].

Or l’évolution de cette intégration peut dépendre de la

gamme de puissance dans laquelle se situe l’application,

définissant la technologie employée. Ainsi, on peut

distinguer l’intégration monolithique dans laquelle les

circuits de commande et de protection sont intégrés avec la

même technologie et dans le même substrat que le

composant de puissance [5,6,7,8,9,1,10] et l’intégration

hybride ou hétérogène dans laquelle la puce de puissance et

son circuit de contrôle sont séparés et le plus souvent issus

de technologies différentes [11,12,4]. Ainsi, pour les tenues

en tension supérieures ou égales à 600V [13,14], les seules

solutions industrielles existantes sont des solutions hybrides

par l’association d’une puce de commande et d’une puce de

puissance haute tension. Pour les tenues en tension

inférieures, il existe des solutions monolithiques où

cohabitent sur une même puce les composants de puissance

haute tension (HVIC) et les composants de commande

basse tension (CMOS) isolés et de technologies différentes

(figure 1) : c’est l’approche Smart Power [15]. On peut

citer, par exemple, la technologie VIPer de ST

Microelectronics particulièrement adaptée aux

convertisseurs mono-interrupteur type flyback (400V, 600V

/ quelques kW).

Bien qu’apportant de nombreuses fonctionnalités, cette

intégration de plusieurs technologies dans le même substrat

entraîne une complexification du procédé technologique,

d’où un plus grand nombre de niveaux de masquage (14 en

2000 pour la technologie VIPer [16-17]). Par ailleurs la

gamme de tension est réduite à la qualité de l’isolation entre

les deux technologies. C’est le principal élément limitant

leur évolution vers les tensions plus importantes. Enfin,

l'approche Smart Power en technologie verticale (fort

courant et forte tension) est habituellement limitée à la mise

en œuvre d'un composant de puissance unique.

Figure 1 : Technologie Smart Power : exemples d’intégration

de différents types de composants (CMOS, DMOS, bipolaire,

mémoires) dans un même substrat [17].

La figure 2 montre un exemple de puce HVIC intégrant

des transistors de puissance latéraux et des circuits de

traitement du signal numériques et analogiques en

technologie CMOS.

On constate que la puce est divisée en deux parties, une

moitié pour la partie ‘puissance’ l’autre pour la partie

‘traitement du signal’. Cette technologie est donc très

performante en termes d’intégration de fonctionnalités,

mais la gamme de puissance accessible est réduite. Ainsi,

les technologies industrielles actuelles, HVIC ou Smart

Power, sont confrontées à des contraintes technologiques

limitant la tension de claquage à quelques centaines de

Volts [18]. C’est pourquoi elles ne sont utilisées que dans le

domaine des faibles puissances, comme dans l'automobile

et les télécommunications.

Figure 2 : Technologie HVIC : exemple d’intégration de

transistors de puissance et de circuits de traitement du signal

analogiques et numériques sur la même puce [5].

III. LE COMPOSANT MONOLITHIQUE

Notre approche vise à simplifier l’approche

monolithique en intégrant sur une même puce et avec une

même technologie verticale les éléments de puissance

(haute tension) et de commande (basse tension). Les

applications visées sont des applications moyennes à hautes

tensions (100V - 3kV), qui présentent des contraintes

élevées d’isolation galvanique ne pouvant pas être

respectées en technologie « Smart Power ». La structure du

cœur de puissance est verticale et les fonctions sont

intégrées dans le même substrat autant que faire ce peut à

l’intérieur d’une région isolée de la haute tension (figure 3).

Figure 3 : Technologie intégration fonctionnelle : exemple de

fonctions intégrables dans la structure de base du composant de

puissance a) vue en coupe d’un ACS et symbole électrique b) vue

en coupe d’un thyristor MOS et symbole électrique [19].

Ce type d’intégration utilise les filières technologiques

des composants de puissance. Elle permet de réaliser de

nombreuses fonctions essentielles comme, par exemple,

une structure MOS pouvant être activée par voie optique

dans [20,8] ou des protections en tension dans [9]. Sans

atteindre la complexité des fonctions obtenues avec les

composants Smart Power, les composants réalisés en

intégration fonctionnelle intègrent toutefois de nombreuses

fonctions de contrôle et de protection autour de l'élément de

puissance.

L’intégration monolithique de puissance poursuit l’effort

d’intégration déjà réalisé sur les composants hybrides afin

d’obtenir une optimisation des interconnexions, de la

fiabilité et de la maîtrise de la CEM. Par ailleurs pour être

économiquement compétitive, l’intégration monolithique

doit être réalisée à bas coût ce qui impose la réalisation des

fonctions avec la même technologie et en même temps que

le cœur de puissance. Cette cohabitation fonction/cœur de

puissance doit s’établir sur une filière technologique

optimisée mais figée afin d’être industrialisable [1]. Ainsi,

autour du cœur de puissance viennent s’ajouter

successivement les fonctions d’isolation optique, le

transformateur sans circuit magnétique [21,22], la structure

de commande rapprochée puis les protections contre les

surtensions et les surintensités [23] tout en minimisant

l’impact sur le procédé de fabrication [24]. Enfin pour

valoriser au mieux les performances de l’intégration

fonctionnelle monolithique, il est nécessaire d’envisager

une approche tridimensionnelle du boitier. Ainsi, la

technique 3D nommée Power Chip On Chip [25] permet un

gain significatif sur les inductances parasites, la CEM

conduite et rayonnée et l’inductance parasite existante au

sein de la cellule de commutation. Toutefois cette approche

repose sur une maîtrise importante des finitions en surface

et périphéries du composant de puissance pour satisfaire

aux contraintes d'empilement des puces de puissance. ADIS

Innovation, en proposant des architectures et des moyens

technologiques innovants, offre une réponse de conception

et de fabrication de composants de puissance pour toutes les

nouvelles applications et exigences de la conversion de

l'énergie électrique

Ainsi, pour être en mesure de réaliser un composant

intégré monolithique industriel sur cahier des charges, il est

nécessaire de disposer :

- d’une filière monolithique de puissance

industrielle qualifiée d’abord en silicium et adaptable

matériaux « grand gap »,

- disposer des méthodes et outils de la

microélectronique transposés à l’électronique de puissance

(EP).

Pour mener à bien son œuvre, ADIS Innovation

s’appuiera sur les travaux des laboratoires LAAS et

G2ELAB notamment sur :

- les réalisations en prototype de fonctions intégrées,

- le développement d’un « design kit » associé à la

technologie de puissance monolithique intégrant

modèles et bibliothèques de fonctions.

Ceci permettra de répondre de manière exhaustive et

efficace aux besoins de nombreux clients intégrateurs.

IV. PERSPECTIVES

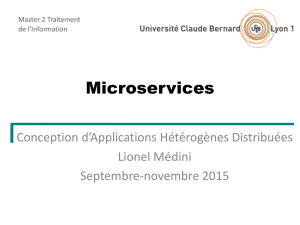

Le cœur technologique d’ADIS Innovation associé à

l’intégration fonctionnelle (figure 4) est en mesure de

répondre à l’attente du marché orienté vers les puissances

croissantes en proposant une solution industrielle intégrée,

fiable et performante pour les applications de demain.

ADIS Innovation validera dès 2012 sa filière à l’aide

d’un premier prototype intégré d’abord sur une technologie

silicium puis déclinera son offre sur les matériaux « grand

gap » tels que le GaN et le SiC.

La mise en œuvre du cœur permet d’envisager la

réalisation de nombreux composants pour différentes

applications dans le domaine de la gestion d’énergie.

Figure 4 : Schéma produit ADIS Innovation : intégration

monolithique sur un même pavé des fonctions autour du cœur

MOS pour répondre aux différents besoins d’intégration,

performances et fiabilité.

V. BIBLIOGRAPHIE

• [1] H.X. Nguyen, “Méthodes et Modèles pour une Approche de

Dimensionnement Géométrique et Technologique d'un Semi-

conducteur de Puissance Intégré. Application à la Conception

d'un MOSFET Vertical autonome”, PhD Thesis, Université de

Grenoble, Octobre 2011.

• [2] M. Marmouget, J-L. Sanchez, P. Austin, M. Breil, T.

Bordignon, V. Houdbert, J. Jalade, “Identification de cellules

élémentaires en intégration fonctionnelle de puissance :

exemples de conception de fonctions intégrées”, Électronique

de Puissance du Futur 1998 (EPF'98). Belfort (France) - 16-18

Décembre 98, pp. 57-62.

• [3] P. Austin, J-L. Sanchez, M. Breil, J-P. Laur, J. Jalade, M.

Marmouget, T. Bordignon, E. Imbernon, O. Causse, G. Bonnet,

B. Rousset, F. Rossel, “Environnement de conception et filière

technologique flexible adaptés au mode d’intégration

fonctionnelle”, EPF 2000, 8e colloque Électronique de

Puissance du Futur, Lille, France, 29 novembre-1er décembre

2000, pp.183-188.

• [4] T Simonot, N Rouger, JC Crébier, V Gaude, “A novel

Power System in Package with 3D chip on chip

interconnections of the power transistor and its gate driver",

IEEE ISPSD’2011, Mai 2011.

• [5] G. Verneau, “Optimisation Géométrique de MOSFETs de

Puissance en vue d’Intégrer l’Alimentation de l’Etage de

Commande “, Thèse de l’Institut National Polytechnique de

Grenoble, Mai 2002.

• [6] C. Caramel, “Nouvelles fonctions interrupteurs intégrées

pour la conversion d'énergie”, PhD Thesis, Université Paul

Sabatier, Avril 2007.

• [7] F. Capy, “Étude et conception d'un interrupteur de puissance

monolithique à auto-commutation: le thyristor dual

disjoncteur”, Thèse Université Paul Sabatier, 2009.

• [8] N. Rouger, “Intégration monolithique des fonctions

d'interface au sein de composants de puissance à structure

verticale ”, PhD Thesis, Université de Grenoble, Juillet 2008.

• [9] L. Vincent, “Contribution à la Conception et Assistance au

Prototypage de Systèmes Intégrés sur Silicium (CAPsis)

Application à l'interrupteur automatique VD-MOSFET”, Thèse

de l’Institut National Polytechnique de Grenoble – INPG, 2010.

• [10] B.D. Nguyen, “Intégration fonctionnelle autour des

composants quatre quadrants avec application à la conversion

AC-AC”, PhD Thesis, Université de Grenoble, Mars 2008.

• [11] T. Simonot, “Conception et hybridation de l'environnement

électronique des composants de puissance à structure verticale”,

PhD Thesis, Université de Grenoble, Novembre 2011.

• [12] T. Stockmeier, P. Beckedahl, C. Gobl, T. Malzer, "SKiN:

Double side sintering technology for new packages," IEEE

ISPSD’2011, pp. 324-327, 23-26, Mai 2011.

• [13] L. Théolier, “Conception de transistors MOS haute tension

(1200 Volts) pour l'électronique de puissance”, Thèse de

l’université Paul Sabatier, 2008.

• [14] T. Bouchet, “Etude de la zone de charge d'espace mixte

(ZCEM) dans le drain des MOS haute tension”, PhD Thesis,

Université de Marseille, Décembre 2001.

• [15] R. De Maglie. “Modélisation de différentes technologies

de transistors bipolaires à grille isolée pour la simulation

Cœur ADIS

Innovation

MOS

V > 100V

I > 1 A

Commandes

Auto

Alimentées

Détecteurs

Température

Détecteurs

Court-

Circuit

Détecteurs

Tension

Drivers

Intégrés

INTEGRATION

vs

Surface

INTEGRATION

vs

Fonctionnalité

Taille et Prix

consommation

énergétique

réduite

Fiabilité

et

Sécurité

Performance

électrique

(τ,I,V)

BESOINS

PRODUIT

ADIS Innovation

GAIN

d'applications en électronique de puissance”, PhD thesis,

Université Paul Sabatier Toulouse III, 2007.

• [16] N. Cézac, F. Morancho, P. Rossel, H. Tranduc, A. Peyre-

Lavigne, A new generation of power unipolar devices : the

concept of the Floating Island MOS Transistor (FLIMOST) »,

Proceedings ISPSD’2000 (Toulouse), pp. 69-72, Mai 2000.

• [17] H. Tahir, “Conception et réalisation de structures IGBTs

bidirectionnelles en courant et en tension”, PhD thesis,

Université Paul Sabatier Toulouse III, 2011.

• [18] F. Bernot,,“Composants de l’électronique de puissance”,

Techniques de l’Ingénieur, 2000.

• [19] M. H. Rashid, “Power electronics handbook: devices,

circuits, and applications”, Academic Press, 2006.

• [20] Y. Patel, J. Jalade, J-L. Sanchez, R. Berriane, J-P Laur, P.

Austin, “Characterisation of a new high voltage integrated

switch: MOS- Gated optically triggered thyristor”, EPE Journal,

Vol.6, n°2, Septembre 1996.

• [21] T. Simonot, N. Rouger, and J.‐C. Crebier, “Design and

characterization of an integrated CMOS gate driver for vertical

power MOSFETs,” in 2010 IEEE Energy Conversion Congress

and Exposition, Atlanta, GA, USA, 2010, pp. 2206‐2213.

• [22] T. Simonot, N. Rouger, and J.C. Crebier, “Conception,

intégration 3D et caractérisation d’un circuit de commande

CMOS pour transistors de puissance,” in Electronique de

puissance du Futur. EPF, Saint‐Nazaire, 2010.

• [23] Fisal Alkayal, “Contribution à l’intégration monolithique

de protections contre les surtensions: application aux

convertisseurs de puissance haute tension,” Mémoire de thèse,

Grenoble INP, 2005.

• [24] D. B. Nguyen, “Intégration fonctionnelle autour des

composants quatre quadrants avec l’application à la conversion

AC/AC,” Mémoire de thèse, Grenoble INP, G2ELab, 2008.

• [25] Eric Vagnon, “Solutions innovantes pour le packaging de

convertisseurs statiques polyphasés,” Mémoire de thèse,

Grenoble INP, 2010.

1

/

4

100%