Circuit logique à seuil et à sécurité intrinsèque

Europâisches Patentamt

European Patent Office ® Numéro de publication: 0138

706

AO

Office européen des brevets n^c-

© DEMANDE DE BREVET EUROPEEN

© Numéro de dépôt: 84402029.7 ® Int. Cl.4: H 03 K 19/007

(g) Date de dépôt: 09.10.84

® Priorite: 13.10.83 FR8316331 © Demandeur: JEUMONT-SCHNEIDERSoci6te anonyme

dite :, 31 -32, Quai de Dion Bouton, F-9281 1 Puteaux

Cedex (FR)

@ Date de publication de la demande: 24.04.85 ^ , * ^ ,,, > . „„

Bulletin 85/17 ® Inventeur: Guillaumin, Jacques, 19-21, rue Henri

Barbusse, F-93260 Les Lilas (FR)

@ Mandataire: Lejet, Christian, Societe

® Etats contractants designes : BE CH DE FR GB IT LI LU JEUMONT-SCHNEIDER 31 -32, Quai de Dion Bouton,

NL F-9281 1 Puteaux Cedex (FR)

Circuit logique à seuil et à sécurité intrinsèque.

CM

<

(O

o

00

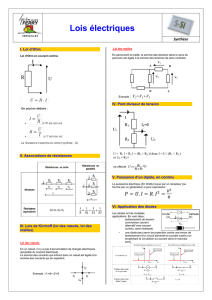

© L'invention concerne un circuit logique à seuil et à sécu-

rité intrinsèque tel que de toute modification des caractéristi-

ques de l'un de ses composants résulte une augmentation

relative de la valeur du seuil. Il comprend un comparateur (7)

à l'une des entrées duquel est appliquée une tension conti-

nue de référence (VR) tandis que l'autre entrée est connec-

tée au point de jonction d'une première et d'une deuxième

résistance (1, 2).

Une première tension continue (V1) de valeur relative

basse est appliquée à l'autre extrémité de la première résis-

tance (1), et une deuxième tension continue (V2) de valeur

relative élevée est appliquée à l'autre extrémité de la

deuxième résistance (2) par l'intermédiaire d'une troisième

résistance (3).

Selon l'invention, on applique au point de jonction (A)

des deuxième et troisième résistances (2, 3) une troisième

tension continue (V3) de valeur relative intermédiaire par

l'intermédiaire d'une quatrième résistance (4) en série avec

un commutateur (6) de hachage.

Application à la signalisation ferroviaire.

V2

B'

V3

Vl

CL

III

ACTORUM AG

L'invention concerne un circuit logique à seuil et à sécu-

rité intrinsèque tel que de toute modification des caractéristi-

ques de l'un de ses composants résulte une augmentation

relative de la valeur du seuil. Il comprend un comparateur (7)

à l'une des entrées duquel est appliquée une tension conti-

nue de référence (VR) tandis que l'autre entrée est connec-

tée au point de jonction d'une première et d'une deuxième

résistance (1, 2).

Une première tension continue (V1) de valeur relative

basse est appliquée à l'autre extrémité de la première résis-

tance (1), et une deuxième tension continue (V2) de valeur

relative élevée est appliquée à l'autre extrémité de la

deuxième résistance (2) par l'intermédiaire d'une troisième

résistance (3).

Selon l'invention, on applique au point de jonction (A)

des deuxième et troisième résistances (2, 3) une troisième

tension continue (V3) de valeur relative intermédiaire par

l'intermédiaire d'une quatrième résistance (4) en série avec

un commutateur (6) de hachage.

Application à la signalisation ferroviaire.

La présente invention concerne un circuit logique à seuil et à sécurité

intrinsèque, possédant au moins une entrée et une sortie et tel que d'au-

cune panne ou modification des caractéristiques du circuit ne peut résulter

un signal de sortie si le seuil n'est pas atteint.

De tels circuits de sécurité sont utilisés en particulier dans la signalisa-

tion ferroviaire dans des détecteurs de passage d'un véhicule sur une

voie ferrée, ce qui leur impose de satisfaire à des normes de sécurité

sévères.

On connaît de tels circuits logiques de sécurité. Par exemple, dans le

brevet français 2 510 845, est décrit un circuit à deux entrées et une

sortie, alimenté entre une tension continue Vcc non nulle et la masse,

comportant en combinaison une pompe à diodes, un sous-ensemble inter-

médiaire et en sortie un transistor monté en émetteur commun. En cours

de fonctionnement, dans certaines conditions, ce circuit peut ne présenter

aucune sécurité. Dans un premier cas, si une coupure de la résistance

située entre le conducteur d'alimentation à la tension Vcc et la base

du transistor de sortie se combine à des fuites entre le collecteur et

la base de ce même transistor, le circuit peut continuer à présenter

un signal en sortie dont l'amplitude est telle qu'elle ne permet pas de

détecter la panne du dispositif ce qui est contraire à la sécurité. Dans

un deuxième cas, une fuite entre la base et l'émetteur du même transistor

de sortie a tendance à s'opposer à la polarisation réalisée par la résistance

mentionnée ci-dessus, ce qui diminue la valeur du seuil, et donc altère

la sécurité du dispositif.

Un but de l'invention est d'obvier à ces inconvénients et de réaliser

un circuit logique tel que toute défaillance dans ce circuit doit conduire

à une augmentation du seuil et donc à un état de sécurité supérieur

à celui qui existait avant l'incident.

Un autre but de l'invention est de réaliser de façon modulaire, à partir

du même circuit logique de base correspondant à un circuit logique "OUI".

des circuits logiques réalisant d'autres fonctions logiques classiques.

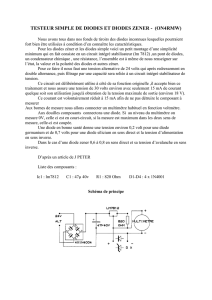

Selon la présente invention, le circuit logique à seuil et à sécurité intrin-

sèque comprend un comparateur à l'une des entrées duquel est appliquée

une tension continue de référence tandis que l'autre entrée est connectée

au point de jonction d'une première et d'une deuxième résistances, une

première tension continue de valeur relative basse étant appliquée à

l'autre extrémité de la première résistance et une deuxième tension

continue de valeur relative élevée étant appliquée à l'autre extrémité

de la deuxième résistance par l'intermédiaire d'une troisième résistance.

On applique au point de jonction des deuxième et troisième résistances

une troisième tension continue de valeur relative intermédiaire par l'inter-

médiaire d'une quatrième résistance en série avec un commutateur de

hachage. Le comparateur est de préférence constitué par un transistor

monté en base commune, à la base duquel on applique la troisième tension

continue ; l'émetteur est relié au point de jonction de la première et de

la deuxième résistances tandis que le collecteur, auquel est appli-

qué la deuxième tension continue par l'intermédiaire d'une cinquième

résistance, constitue la sortie du comparateur. De préférence ce transistor

est du type npn, la première tension étant négative, la deuxième tension

ayant une valeur positive tandis que la troisième est nulle. On peut toute-

fois inverser les diverses polarisations en utilisant un transistor pnp.

Pour mettre en oeuvre ce circuit avec un signal alternatif, on dispose

une première pompe à diodes à l'entrée de manière à transformer ce

signal alternatif en la première tension continue.

Ce circuit inclut de préférence, un dispositif de compensation en tempé-

rature comprenant une pluralité de diodes connectées de telle manière

qu'elles soient dans le sens passant et en série entre le point de jonction

des troisième et quatrième résistances et la deuxième résistance.

Le circuit logique décrit ci-dessus permet de réaliser d'autres circuits

logiques de sécurité réalisant notamment les fonctions logiques "ET"

et "OU".

Un circuit logique "ET" pour deux signaux alternatifs est réalisé en pi-

lotant le commutateur du circuit logique "OUI" par un signal alternatif,

l'autre étant appliqué à la pompe à diodes précitée.

Un circuit logique "OU" pour plusieurs signaux alternatifs est obtenu

en branchant plusieurs pompes à diodes en parallèle avec la première

pompe à diodes du circuit logique "OUI".

Un circuit logique "ET" pour plusieurs signaux alternatifs est obtenu

en branchant plusieurs pompes à diodes en série avec la première pompe

à diodes du circuit logique "OUI" et en augmentant en conséquence la

valeur du seuil du circuit.

Pour l'un quelconque des circuits logiques décrits, le collecteur du tran-

sistor est de préférence relié à un amplificateur de courant constitué

par deux transistors montés en collecteur commun et de types complémen-

taires, dont la réunion des bases en constitue l'entrée et celle des émet-

teurs la sortie tandis qu'à leurs collecteurs sont respectivement appliquées

les deuxième et troisième tensions continues.

La présente invention sera mieux comprise et d'autres buts, avantages

et caractéristiques de celle-ci apparaîtront plus clairement à la lecture

de la description qui suit d'un mode de réalisation de l'invention, descrip-

tion à laquelle trois planches de dessins sont annexées.

La Figure la est le schéma électronique d'un circuit logique de base

selon l'invention et la figure lb est un diagramme de temps de certains

signaux apparaissant dans le circuit, servant à expliciter son fonctionne-

ment.

La Figure 2 est le schéma électronique du circuit logique représenté

Figure la où un transistor monté en base commune a été substitué au

comparateur.

La Figure 3 est le schéma électronique du circuit logique précédent

auquel est adjointe une pompe à diodes sur l'entrée du circuit à laquelle

est appliqué un signal alternatif.

La Figure 4 est le schéma électronique du circuit logique selon la figure 2

perfectionné par un dispositif de compensation en température.

La figure 5 est le schéma électronique d'un circuit logique "OU" pour

deux signaux alternatifs selon l'invention.

La figure 6 est le schéma électronique d'un circuit logique "ET" pour

deux signaux alternatifs selon l'invention.

La figure 7 montre une interface possible du circuit logique représenté

figure 2 avec d'autres circuits, cette interface réalisant une amplification

en courant.

En référence maintenant à la figure la qui représente un mode de réalisa-

tion du circuit logique selon l'invention, la tension continue de valeur

relative basse est choisie négative (VI), celle de valeur relative élevée

est choisie positive (V2) et celle de valeur intermédiaire est choisie nulle

(V3).

Le commutateur 6 est relié d'une part directement à la masse (V3) et

d'autre part par l'intermédiaire des deux résistances 3 et 4 à la tension

V2. Le commutateur hache le courant dans ces deux résistances et crée

au point de jonction A de ces deux résistances 3 et 4 un signal en forme

de créneau de tensions extrêmes V2 et KV2, K étant fonction .des valeurs

des résistances 3 et 4 et inférieur à 1.

Si le commutateur 6 reste ouvert, la tension VA croît et aucun signal

en forme de créneau n'est transmis au comparateur 7 qui délivre alors

en sortie un signal continu. Il en est de même si la résistance 4 est cou-

pée. Si la résistance 3 est coupée,, la tension VA chute et le signal en

forme de créneau ne présente plus une amplitude suffisante pour faire

commuter le comparateur 7. Si la résistance 2 est coupée, bien évidem-

ment aucun signal n'est transmis au comparateur 7.

On constate donc que ce circuit présente bien la sécurité intrinsèque

requise notamment parce que le signal utile appliqué au comparateur

7 doit être la somme d'un signal en forme de créneau et d'une tension

continue et doit présenter une amplitude déterminée comprise entre

deux bornes pour que le comparateur 7 puisse assurer sa fonction.

Un comparateur 7 est disposé de manière qu'à l'une de ses entrées soit

appliquée une tension de référence V R tandis que son autre entrée est

reliée au point de jonction B de deux résistances 1 et 2. A l'autre extré-

mité E de la résistance 1 est appliquée la tension négative VI tandis

que l'autre extrémité de la résistance 2 est reliée au point A précité.

Le comparateur 7 comporte une sortie S qui constitue la sortie du circuit

logique.

Ce signal en forme de créneau est alors transmis du point A au point

B par la résistance 2. La tension négative VI appliquée au point E est

transmise au point B par la résistance 1. Il apparaît donc au point B

un signal créneau de tensions extrêmes U et V, U et V étant fonction-

des tensions VI, V2 et des résistances 1,2,3, et 4.

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

1

/

15

100%