AFAF - Polytechnique Montréal

Polytechnique Montréal page 1/2 Département de génie informatique et génie logiciel

INF3500 – Hiver 2017

Devoir #10 – Performance : le temps

1001 Introduction

1. On désire filtrer les images d’une vidéo HD 1980 × 1080 @ 60 fps. Le filtrage désiré consiste à rem-

placer chaque pixel par la moyenne des 8 pixels qui l’entourent.

a. Quel est le taux de traitement requis en pixels/s pour effectuer un traitement en temps réel?

b. Si les opérations arithmétiques nécessitent 1 cycle d’horloge en moyenne, quelle est la fréquence

d’horloge requise pour effectuer le traitement en temps réel?

c. Si chaque opération arithmétique nécessite 1 cycle d’horloge en moyenne et que la fréquence

d’horloge est de 185 MHz, combien d’unités de traitement en parallèle sont nécessaires?

1002 Temps de propagation

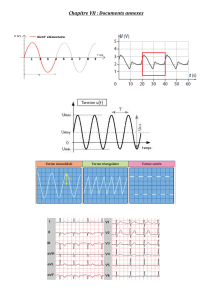

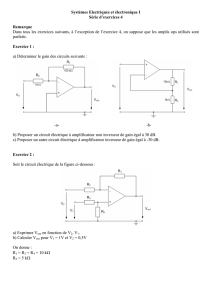

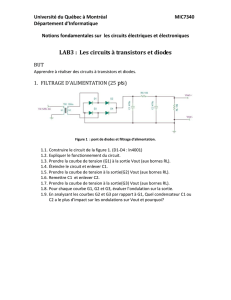

2. Supposez un inverseur dont l’entrée A est une onde carrée de période 14 ns. Dessinez une onde de

sortie F avec un tPHL de 3 ns, un tPLH de 4 ns, un tr de 4 ns et un tf de 2 ns.

t (ns)

A

F

5 V

5 V

t (ns)

50%

90%

10%

AF

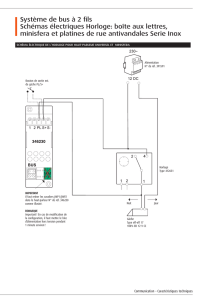

3. Considérez le modèle suivant pour un inverseur dont la sortie est initialement un 0 logique, corres-

pondant à une tension Vout = 0 volt. À t = 0 s, l’entrée de l’inverseur passe instantanément de 1 à 0 lo-

gique. La sortie doit alors passer de 0 à 1 logique, donc on aura éventuellement Vout = VDD volt. On peut

modéliser cette situation par le circuit suivant, pour lequel l’équation de la tension de sortie est : Vout =

VDD × (1 – e-t/RC), où R et C sont respectivement les résistances et capacités du circuit, dues aux transis-

tors et interconnexions, et t est le temps.

a. Donnez une expression pour la valeur du délai de montée tPLH en fonction de R et C.

b. Quel est l’effet sur tPLH de doubler la valeur de R en maintenant C constante?

c. Quelle est la valeur de tPLH pour R = 10 Ω et C = 1 nF?

INF 3500 : Conception et réalisation de systèmes numériques

Polytechnique Montréal page 2/2 Département de génie informatique et génie logiciel

1003 Chemin critique et fréquence maximale d’horloge et 1004 Déphasage d’horloge

4. Le diagramme suivant montre un circuit implémenté sur un FPGA simplifié. Les entrées du circuit

sont les signaux A, B, C, D, E et F. Il y a deux sorties P et Q. Le FPGA est composé de tranches ayant

chacune une table de correspondance (LUT) et une bascule pouvant être utilisée ou non, et de blocs

d’entrée/sortie (IOB) dans lesquels les bascules sont toujours utilisées. Les LUTs ont un délai de 2.25 ns.

Les bascules ont un délai de 0.75 ns, un temps de préparation tsu de 0.25 ns, et un temps de maintien th de

0.1 ns. Les interconnexions ajoutent un délai de 0.2 ns pour chaque rangée et chaque colonne de distance.

Par exemple, le signal qui part de la tranche C0R2 (colonne 0, rangée 2) pour aller à la LUT de la tranche

C1R1 a un délai de (1 (colonnes) + 1 (rangée)) × 0.2 ns = 0.4 ns.

Identifiez le chemin critique du circuit sur le diagramme et donnez la fréquence maximale d’horloge.

C

R

VDD

fermé à t=0

Vout

1

/

2

100%