Manipulation n°1

1

FILIERES : SMP - Option électronique

Semestre 6

Année universitaire 2014-2015

Réalisé par les : P

Pr

r.

.

A

Ab

bd

de

el

ll

la

ah

h

R

RE

EZ

ZZ

ZO

OU

UK

K

Pr. KARIM Mohammed

2

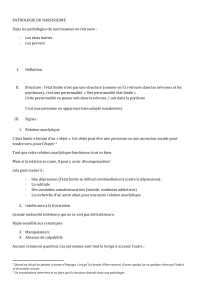

QUELQUES CONSEILS 3

Manipulation n°1 : Logique combinatoire 4

Manipulation n°2 : Circuits Logiques MSI 12

Manipulation 3 : Logique séquentielle, Compteurs Asynchrones 13

Manipulation n°4 : Logique séquentielle, Compteurs Synchrones - Registres 19

3

Quelques conseils

La préparation du TP

La préparation du TP est importante. Vous devez, avant de venir en TP, avoir préparé votre travail, c'est à

dire avoir rédigé la partie théorique du TP. De plus, la préparation ne doit pas se faire en prenant exemple

sur le travail d'un autre binôme.

Votre comportement en TP, c'est à dire votre autonomie, la façon dont vous résolvez les problèmes, votre

efficacité est prise en compte dans la note.

Le compte-rendu :

Le compte-rendu doit comporter pour chaque exercice:

Une partie théorique,

Une partie pratique : un ou des schémas électroniques.

Une analyse des résultats obtenus.

Enfin, la présentation en elle-même de tout travail est importante.

Le contrôle :

Le contrôle a lieu à la fin des TPs. Il dure 1h et sera individuel. Le contrôle compte pour ¾ dans la note

finale des Travaux Pratiques.

Fascicule TP en ligne :

Site : http://www.fsdmfes.ac.ma/ (voir ressources pédagogiques/filière SMP/S6)

4

Manipulation n°1 : Logique combinatoire

L’objectif de cette manipulation est de réaliser un circuit logique combinatoire à base de portes logiques

standard (NOT,AND,OR,NAND,NOR,XOR) selon un cahier des charges pré-établi. Vous allez traiter dans

cette manipulation tous les circuits logiques combinatoires à savoir les circuits arithmétiques, les circuits

de décodage et de multiplexage.

Vous allez utiliser un logiciel « Digital » qui vous permet de réaliser des circuits logiques combinatoires et

séquentiels et d’analyser leur fonctionnement.

Les portes logiques

1. Inverseur : fonction NOT

La fonction NOT appelée couramment inverseur a une seule entrée et une seule sortie. La

sortie d'un inverseur prend l'état 1 si et seulement si son entrée est dans l'état 0. Son

fonctionnement est défini par la table de vérité suivante :

A

AAf )(

0

1

1

0

Symbole graphique d’inverseur

En pratique, l’inverseur est implanté dans le circuit intégré TTL 7404 qui comprend six

inverseurs (figure n°1). J’ai retenu la technologie TTL (Transistor Transistor Logic) qui demeure

5

celle que l’on retrouve souvent dans les applications. La technologie TTL, désignée par la série

74XX et commercialisée en 1964 par Texas Instruments, fonctionne sous une tension

d’alimentation de + 5 V (Vcc) par rapport à la masse (GND).

Figure n°1

2. Fonction OR

La fonction OR, encore appelée addition logique, a deux entrées. La sortie d'une

fonction OR est dans l'état 1 si au moins une de ses entrées est dans l'état 1. La fonction OR,

notée +, est définie par la table de vérité suivante :

A

B

BAf

0

0

0

0

1

1

1

0

1

1

1

1

Une porte logique OR à deux entrées est symbolisée de la manière suivante :

La fonction OR est implantée dans le CI 7432 qui comprend 4 portes logiques OR à deux

entrées (figure n°2).

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

1

/

19

100%