Interruptions : Structure et Applications des Ordinateurs

GIF-1001

Cours 10, p.1

Etienne Tremblay

Ordinateurs, Structure

et Applications

GIF-1001

Université Laval, Hiver 2014

Cours 10, Les interruptions

GIF-1001

Cours 10, p.2

Les interruptions

• Une interruption interrompt l’exécution séquentielle des instructions par le

microprocesseur. Lors d’une interruption, l’exécution du programme

principal est suspendue. Une sous-routine traitant l’interruption est

exécutée, puis le programme principal est continué.

– Les sauts conditionnels ou inconditionnels ainsi que les appels de sous-routines

ne sont pas des interruptions. Cependant, un appel de sous-routine ressemble

beaucoup à une interruption avec une différence fondamentale: les interruptions

peuvent survenir n’importe quand pendant l’exécution.

GIF-1001

Cours 10, p.3

Les interruptions

• Les interruptions peuvent avoir plusieurs sources ou causes dans un

ordinateur. Un numéro est associé à chaque interruption:

– Les périphériques peuvent générer des interruptions. On parle d’interruption matérielle.

– Le processeur peut générer des interruptions s’il n’est pas capable de lire ou d’exécuter une

instruction (opcode invalide, division par 0, mémoire protégée, etc). Dans la littérature, le

terme « Exception » est parfois utilisé pour décrire ce type d’interruption ou pour décrire

l’ensemble des interruptions.

– Le système peut générer des interruptions: reset, NMI (non-maskable Interrupt), faute

matérielle générale, etc.

– Le programme peut générer des interruptions. Il y a une instruction qui permet « d’appeler »

une interruption dans tous les jeux d’instructions. Ce sont des interruptions logicielles.

– Il y a des interruptions pour le debug...

• Les interruptions de l’ordinateur sont gérées par le contrôleur d’interruption.

Ce dernier permet d’activer (masquer) ou de désactiver certaines

interruptions. Il permet aussi de changer la priorité des interruptions.

– Le contrôleur d’interruption est souvent inclus dans le chipset. Dans le cas du processeur

ARM, le contrôleur d’interruption (NVIC) est inclus dans le cœur.

– Le contrôleur d’interruption mémorise les interruptions qui se produisent dans le système.

• Les interruptions ont des priorités: une interruption haute-priorité peut

interrompre une interruption ayant un niveau de priorité plus bas.

– Certaines interruptions peuvent survenir n’importe quand, même pendant une autre

interruption.

– Certaines interruptions, comme reset, ont une priorité qui ne peut pas être changée.

– Habituellement, l’interruption la plus prioritaire est l’interruption Reset. Ensuite, les

interruptions systèmes sont les plus prioritaires, afin les interruptions logicielles sont plus

prioritaires que les interruptions matérielles qui sont les moins prioritaires.

GIF-1001

Cours 10, p.4

Une interruption se produit…

• Lors d’une interruption, les évènements suivants se produisent:

– Le microprocesseur termine le(s) instruction(s) en cours.

• Dans un pipeline d’instruction, plusieurs instructions sont en cours et la gestion des interruptions doit

être faite soigneusement.

– Le microprocesseur ou le contrôleur d’interruptions vérifie si l’interruption peut

être traitée.

• L’interruption peut être masquée (désactivée) ou ne pas être exécutée parce qu’une autre interruption

de priorité supérieure ou égale est en cours. L’interruption est mise de côté pour être exécutée

ultérieurement (lorsqu’elle sera réactivée ou lorsque l’interruption de priorité >= finira.

– Le microprocesseur sauvegarde l’adresse de retour et les drapeaux pour

permettre de reprendre l’exécution après le traitement de l’interruption.

• La sauvegarde se fait automatiquement sur la pile.

– Le microprocesseur sauvegarde certains de ses registres pour accélérer le

traitement de l’interruption.

• La sauvegarde se fait automatiquement sur la pile.

– Le microprocesseur détermine l’adresse de la routine qui traitera l’interruption

(ISR ou Interrupt Service Routine). Cette routine est en mémoire code.

• Voir acétate suivante.

– Le microprocesseur met PC = Adresse de l’ISR.

• La lecture et l’exécution d’instructions continue dans l’ISR.

GIF-1001

Cours 10, p.5

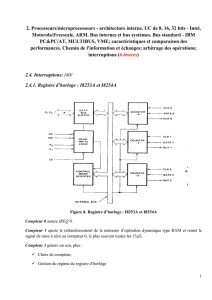

Interruptions vectorisées

• La table des vecteurs d’interruption contient l’adresse de la sous-routine à exécuter

lorsqu’une interruption survient. Pour chaque interruption, la table contient l’adresse

de l’ISR. Chaque entrée de la table est un “vecteur” qui mène aux instruction à

exécuter pour traiter l’interruption.

• La table des vecteurs d’interruption commence habituellement à l’adresse 0h de la

mémoire (Ne pas mettre de code à cet endroit!). La table des vecteurs d’interruption

est habituellement en mémoire FLASH (contenu décidé par le

compilateur/programmeur), mais elle peut habituellement être relocalisée en RAM ou

modifiée par le système d’exploitation.

• Lorsqu’une interruption survient, le numéro de

l’interruption permet de trouver l’emplacement

des instructions à exécuter. Ce numéro sert

d’index dans la table des vecteurs d’interruption.

• Dans la mémoire, le numéro de l’interruption est

multiplié par 4 afin de trouver l’adresse de

l’adresse de l’ISR quand la table commence à

l’adresse 0 et que les adresses ont 32 bits...

# d'INT Contenu

0 Adresse de la routine à exécuter quand l'INT 0 survient

1 Adresse de la routine à exécuter quand l'INT 1 survient

2 Adresse de la routine à exécuter quand l'INT 2 survient

3 Adresse de la routine à exécuter quand l'INT 3 survient

… …

Table des vecteurs d'interruption

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

1

/

16

100%