Introduction

Page 1

Introduction

I DEFINITION D'UN MICRO-PROCESSEUR

_ logique combinatoire : la sortie ne dépend que des entrées

(c'est une combinaison : ET , OU ...)

E S S = f ( E )

_ logique séquentielle : la sortie dépend des entrées et de l'état précédent de la sortie

( c'est la notion de mémoire )

E

S S = f ( E , S )

ici intervient le temps

_ logique programmée : la sortie dépend des entrées et la fonction réalisée dépend du

code ou "instruction"

code binaire

E S S = f ( E , code )

le code binaire détermine la fonction qui est réalisée

TECHNOLOGIE

_ SSI : Small Scale Intégration : portes logiques

_ MSI : Médium Scale Intégration : multiplexeurs, demultiplexeurs, compteurs

_ LSI : Large Scale Intégration : mémoires

Microprocesseur

Feuray

Sciences

de l’ingénieur

2011-2012

µP 1µP 1

_ système minimum

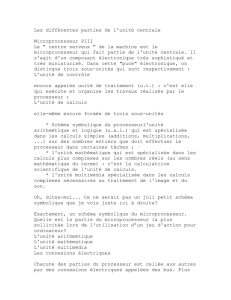

II CONSTITUTION D'UN SYSTEME A µP

Page 2

µP 1µP 1 Introduction

Micro-

processeur

Horloge

Interface

d'entrée

sortie

Mémoire

de

Données

Mémoire

de

Programme

bus d'adresse : m = 16

bus de données : n = 8

bus de contrôle

ROM mémoire programme

Horloge

Unité

Entrées centrale Sorties

de

traitement

RAM

mémoire des données

Microprocesseur

Sciences

de l’ingénieur

2011-2012

Page 3

Introduction

III DEFINITIONS

HORLOGE : signal périodique binaire (signal carré) qui définit la vitesse

de fonctionnement du µP et qui synchronise les circuits entre eux

MICROPROCESSEUR (µP) : traitement des données binaires, effectuée par des

opération arithmétiques et logiques. Ces opérations sont appelées "instructions".

Les instructions sont des mots de 8 bits appelés "octets".

MEMOIRES : reçoit et retient les informations nécessaires à l'exécution du traitement

numérique, les restitue ensuite sur demande.

16

ADRESSE : permet de sélectionner une case mémoire parmi les 2 contenues dans la

mémoire (mot de 16 bits : bus d'adresse).

ORGANE ENTREE SORTIE : permet de transférer un mot binaire depuis le µP vers

l'extérieur, ou l'inverse. Ce transfert utilise le bus données.

BUS : ensemble de conducteurs : reliant un générateur avec un ou plusieurs récepteurs.

_ bus de données : bidirectionnel

n bit : 8, 16 ou 32

_ bus d'adresse : unidirectionnel

m bit : 16, 20, 24 ou 32

_ bus de commande :

* lecture / écriture ( R / W )

* validation des adresses ( VMA )

* horloge ( E )

* reset ( RST ou RESET )

* demande d'interruption ( IRQ )

de quelques Mhz

Microprocesseur

Sciences

de l’ingénieur

2011-2012

µP 1µP 1

Page 4

Introduction

IV CAPACITE D'ADRESSAGE

_ 1 octet ou byte = 8 bits

m

_ capacité = 2 mots avec m nombre de lignes d'adresses

ex: 6809 :

* m = 16 16

* n = 8 ---> 2 mots (de 1 octet) = 65 536 octets = 64 Ko ( 1K = 1024 )

ex: 68000 :

* m = 24 24

* n = 16 ---> 2 . mots (de 2 octets) = 32 Mo

ex : 68020 :

* m = 32 32

* n = 32 ---> 2 . mots (de 4 octets) = 16 Go

V CARTOGRAPHIE MEMOIRE (memory map)

FFFF

-------------------

ROM

-------------------

libre

-------------------

Périphériques 64 Ko

-------------------

libre

-------------------

RAM

-------------------

0000

Microprocesseur

Sciences

de l’ingénieur

2011-2012

µP 1µP 1

Page 5

Introduction

VI EVOLUTION DES MICROPROCESSEURS

_ augmentation des largeurs de bus (données ou adresses)

_ augmentation des vitesses de fonctionnement (horloge)

_ diminution des Wait State : le µP attend que la mémoire réponde (Hand Shaking)

_ intégration d'unité de calcul en Flottant (FPU) :

coprocesseur de calcul : intégré dans le µP à partir du 486 DX

_ augmentation des largeurs de registres internes

_ amélioration de la gestion mémoire : Cache

_ mode d'adressage de plus en plus performant

PROCESSEUR CISC : Complex Instruction Sélection Computer

PROCESSEUR RISC : Reduce Instruction Sélection Computer

VII MICRO - CONTROLEURS

Motorola :

_ 6805 : Rom

_ 68705 :

* Eprom

* Ram

* Port I/O parallèle

* Temporisateur (Timer) Programmable

_ 68HC11 :

* Cpu

* Eprom (8Ko - 12Ko)

* Ram (256 à 512 o)

* E²prom (512 o)

* Port I/O parallèle

* Port I/O série asynchrone (ACIA) : communication avec un PC

* Port I/O série synchrone

* chien de garde (COP)

* Temporisateur (Timer) Programmable

_ 683.. : à base de Cpu 68020

_ 68331

_ 68332

* incorporation de PWM

Microprocesseur

Sciences

de l’ingénieur

2011-2012

µP 1µP 1

1

/

5

100%