COMMANDE D`UN MOTEUR A COURANT CONTINU VIA FPGA

REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE

N° d’ordre : ….

Série : …. Mémoire

Présenté en vue de l’obtention du

Diplôme de Master en

Electrotechnique

Option

Electrotechnique

Thème

COMMANDE D’UN MOTEUR A COURANT

CONTINU VIA FPGA

Présenté par :

DERGHAL Smail

Encadreur :

Dr. MEHAZZEM Fateh

Devant le jury :

Président : Dr. KAIKAA Mohamed yazid

Examinateurs : Prof. KHEZZAR Abdelmalek

Dr. BABAA Fatima

Membre de jury : Prof. KERDOUN Djallel

Soutenue le 17/06/2015

MINISTERE DE L’ENSEIGNEMENT SUPERIEUR

ET DE LA RECHERCHE SCIENTIFIQUE

UNIVERSITE DES FRERES MENTOURI CONSTANTINE

Faculté des Sciences de la Technologie

Département : Electrotechnique

CHAPITRE II : Commande Des Moteurs à Courant Continue Via Les Hacheurs

Commande d’un MCC via FPGA

1

Remerciements

CHAPITRE II : Commande Des Moteurs à Courant Continue Via Les Hacheurs

Commande d’un MCC via FPGA

2

Dédicace

CHAPITRE II : Commande Des Moteurs à Courant Continue Via Les Hacheurs

Commande d’un MCC via FPGA

1

SOMMAIRE

Introduction générale

CHAPITRE I : Prototypage rapide sous FPGA - SYSGEN

1. Introduction ................................................................................................................................................ 2

2. Les FPGA .................................................................................................................................................. 2

2.1. L’architecture .................................................................................................................................... 3

2.2. Historique .......................................................................................................................................... 4

3. Le langage de programmation VHDL ....................................................................................................... 5

3.1. Définition du VHDL ........................................................................................................................... 5

3.2. Historique de VHDL .......................................................................................................................... 5

3.3. Structure d'un module VHDL (Unité de conception) ......................................................................... 5

3.4. Notions de base................................................................................................................................... 5

3.5. Syntaxe ............................................................................................................................................... 7

3.6. Les instructions port et generic ........................................................................................................... 7

3.7. Les directions...................................................................................................................................... 7

3.8. Les objets ............................................................................................................................................ 7

3.9. Notation des littéraux ......................................................................................................................... 8

3.10. Les types principaux en synthèse ................................................................................................... 8

3.11. Les bibliothèques ............................................................................................................................ 8

3.12. Les opérations dans VHDL ........................................................................................................... 9

3.13. Les types manipulés par VHDL .................................................................................................. 10

3.14. Les constantes ............................................................................................................................... 10

3.15. Les variables ................................................................................................................................. 10

3.16. Les signaux ................................................................................................................................... 11

3.17. Les commentaire en VHDL .......................................................................................................... 11

3.18. Les processus ............................................................................................................................... 11

3.19. Les principales caractéristiques du langage VHDL ..................................................................... 12

Un langage s'appliquant à plusieurs niveaux de descriptions ................................... 12 3.19.1.

Fonctionnement concurrent ...................................................................................... 12 3.19.2.

Fonctionnement séquentiel ....................................................................................... 13 3.19.3.

3.20. Différences entre un langage de programmation et VHDL ......................................................... 13

4. Modèle System Generator ....................................................................................................................... 14

4.1. Brève description ............................................................................................................................. 14

CHAPITRE II : Commande Des Moteurs à Courant Continue Via Les Hacheurs

Commande d’un MCC via FPGA

2

4.2. Méthode de développement ............................................................................................................. 14

4.3. Simulink .......................................................................................................................................... 14

4.4. Xilinx System Generator ................................................................................................................. 15

5. Conclusion ................................................................................................................................................ 18

CHAPITRE II : Commande des Moteurs à Courant Continue via Les Hacheurs

1. Introduction .............................................................................................................................................. 20

2. La Machine à Courant Continu (MCC) ................................................................................................... 20

2.1. La Force électromotrice (f.e.m.) E ................................................................................. 21

2.2. Couple électromagnétique .............................................................................................. 21

2.3. Le moteur à excitation indépendante ............................................................................ 21

2.3.1. Modèle électrique .......................................................................................................... 21

2.3.2. Bilan énergétique et rendement ..................................................................................... 22

2.4. Le moteur à excitation série .......................................................................................... 22

2.4.1. Modèle électrique .......................................................................................................... 22

2.4.2. Bilan des puissances et rendement ................................................................................ 23

2.5. Quelques considérations pour le moteur à courant continu .......................................... 23

2.5.1. Utilisation des moteurs à courant continu ..................................................................... 23

2.5.2. Démarrage des moteurs à courant continu ..................................................................... 23

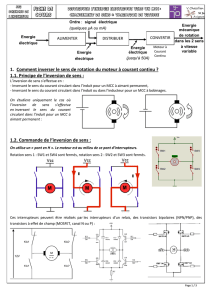

3. LES HACHEURS ................................................................................................................................... 24

3.1.Les interrupteurs électroniques ........................................................................................... 24

3.1.1. Le transistor bipolaire .................................................................................................... 24

3.1.2. Transistor MOSFET ...................................................................................................... 25

3.1.3. GTO ............................................................................................................................... 26

3.1.4. IGBT .............................................................................................................................. 26

3.1.5. La diode à jonction ........................................................................................................ 26

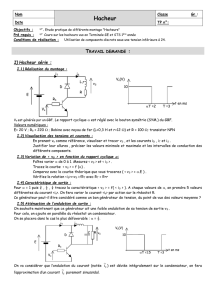

3.2. Hacheur série (abaisseur) .............................................................................................. 27

3.2.1. Principe de fonctionnement ........................................................................................... 27

3.2.2. Etude du hacheur série alimentant un moteur à courant continu .................................. 28

3.3. Hacheur parallèle (Elévateur) ....................................................................................... 29

3.4. Hacheur réversible ........................................................................................................ 32

3.4.1. Hacheur réversible en courant ....................................................................................... 32

3.4.2. Hacheur réversible en tension ........................................................................................ 33

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

1

/

80

100%