Transparents - indico in2p3

QUELLES TECHNOLOGIES

POUR NOS EXPÉRIENCES

P. Pangaud –R. Fei - CPPM

Remerciements à Samuel Manen

Journées VLSI - FPGA - PCB de l'IN2P3 5 -7 juin 2012 Lyon 1P.Pangaud - CPPM

Evolutions des technologies

•Al’IN2P3, depuis 20 ans, le développement de nos

expériences de physiques nous a permis de suivre

l’évolution des technologies monolithiques

- Intégration

- Coût

- Résistance aux Radiations

- Accessibilité

- Production

Journées VLSI - FPGA - PCB de l'IN2P3 5 -7 juin 2012 Lyon P.Pangaud - CPPM 2

Evolutions des technologies

Journées VLSI - FPGA - PCB de l'IN2P3 5 -7 juin 2012 Lyon P.Pangaud - CPPM 3

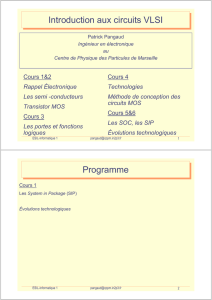

CMOS Feature Size

AMS 0.8µ

1.2k gates/mm2

AMS 0.6µ

3k gates/mm2

ST 0.25µ

35k gates/mm2

AMS 0.35µ

18k gates/mm2

ST 0.18µ

80k gates/mm2

ST 0.13µ

180k gates/mm2

ST 90nm

400k gates/mm2

•High density

•Low power

•More system Integration

•More Process Features

ST 65nm

800k gates/mm2

ST 40nm

1600k gates/mm2

Modélisation des technologies

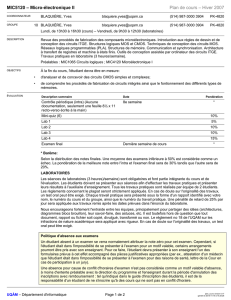

•Les technologies CMOS simplement modélisées à leurs début

•Model Spice 1, 2, 3 ( proches du modèle physique ~40 paramètres).

Tension de seuil (Vt0)

Epaisseur d’oxyde (Tox)

Mobilité (µ0)

Potentiel de Surface (Phi)

Body effect (Gamma)

Bruit I/F (AF et KF)

fonctionnaient très bien en forte inversion sans tenir compte des effets du 2nd

ordre.

•Les modèles BSIM 3, 4 SOI et 6 sont bien mieux adaptés pour les technologies

plus fines, car intégrant beaucoup plus de paramètres de corrections, au

détriment de la complexité. (plus de 400 paramètres).

Journées VLSI - FPGA - PCB de l'IN2P3 5 -7 juin 2012 Lyon P.Pangaud - CPPM 4

Utilisation des technologies

•Beaucoup de cellules fait-main en « full-custom » pour les technologies

jusqu’à 0,35µm, que cela soit pour l’analogique ou le numérique.

•L’intégration a favorisé l’émergence de nouveaux outils d’aide à la

conception, permettant la réutilisation des cellules (analogiques) et la

synthèse de cellules numériques. Des bibliothèques existent (ARM, Synopsys,

Aragio, etc…).

•La notion de Rad-Tolérant à presque disparue à partir du nœud 0,13µm, pour

quasiment disparaître à partir de 65nm. Les effets d’interfaces dominent par

rapport aux effets de grille. Les effets de variations de Vt0 en fonction de la

dose s’estompent. Par contre, la qualité de la technologie devient essentielle

(dopage, épitaxie, STI..).

Journées VLSI - FPGA - PCB de l'IN2P3 5 -7 juin 2012 Lyon P.Pangaud - CPPM 5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

1

/

12

100%