Registres

Les

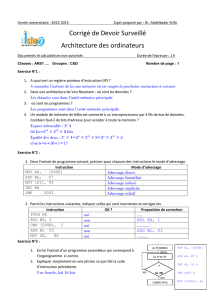

m

P 80x86 d’Intel : histoire et

caractéristiques

1.Rappel historique Bref sur la famille 80x86

2. A l’intérieur du mP 8088/8086

3. Introduction a la programmation Assembleur

4. Segmentation des programmes

5. Modes d’Adressage

1Rappel historique Bref sur la famille 80x86

-Évolution de 8080/8085 à 8086:

En 1978, Intel introduit le mP8086 à16-bit, qui améliore les performances de la série mP8080/85

de plusieurs façons.

-Le mP 8086 possède 16 lignes d’adresses (64Ko de mémoire), alors que le

mP 8080/8085 en possède 8 lignes d’adresses (256 octets).

-Le mP 8080/8085 a une architecture 8-bit, i.e. les données de plus de 8bits sont

traitées en morceaux de 8-bits par la CPU. Alors que le 8086 est un mP à16-bits.

-Le mP 8086 est de conception pipeline contrairement au mP 8080/8085. Dans un

système à base de pipeline, les bus de données et d’adresses sont occupés à

transférer des données pendant que la CPU traite une information. Ceci a pour

avantage de croître la puissance de traitement du mP.

-Évolution de 8086 a 8088:

-Le mP 8086 a une architecture interne et externe de 16-bit, i.e. tout ses registres sont

de 16-bits et un bus de données également de 16-bits pour transférer des données de/vers la CPU.

-Le mP 8086 a marqué une grande avancée par rapport aux générations précédentes,

mais il a rencontré une résistance d’utilisation du au fait que son bus de données externe de 16-bits

ne prêtait pas aux périphériques existants en ce moment conçus pour des mP à 8-bits. En plus du

fait que les cartes de circuits imprimés avec un bus de données 16-bits étaient chères.

- Ceci explique pourquoi Intel a conçu le mP8088, qui est le même que le mP8086 au

niveau de la programmation avec la même capacité mémoire, 1Mo. Seulement son bus de données

externe est 8-bits au lieu de 16-bits.

1Rappel historique Bref sur la famille 80x86

-Succès du mP 8088:

La situation financière d’Intel s’est considérablement amélioré lorsque IBM a choisi le 8086

comme le mP de choix pour son micro-ordinateur IBM PC, qui a connu un énorme succès, a

cause du fait qu’IBM et Microsoft (qui a développé MSDOS), l’ont rendu système ouvert, i.e.

la documentation hardware et software du PC est accessible au public. Ceci a permis aux

autres vendeurs de cloner le hardware avec succès.

-Le mP 80286

-Avec le succès qu’a connu Intel et devant le besoin manifeste des utilisateurs PC

pour un mP plus puissant, Il a introduit le mP 80286 en 1982. Ses principales caractéristiques

sont: un bus de donnes interne et externe de 16-bit, un bus d’adresses de 24-bit (ciblant

16Mbytes de mémoire), et surtout sa mémoire virtuelle.

-Le mP 80286 opère en 2 modes: réel et protégé. Le mode réel n’est autre que la

version rapide du mP 8088/8086 avec la même mémoire de 1Mo. Le mode protégé permet

d’adresser une mémoire de 16Mo, mais aussi capable de protéger le OS et programmes d’une

destruction accidentelle par l’utilisateur. Cette caractéristique est absente avec le mP 8088/86.

- La mémoire virtuelle est une façon de tromper le mP en pensant qu’il a accès a une

mémoire illimité en inter-changeant les données entre le disque et la RAM.

- IBM a choisi le mP 80286 pour son micro-ordinateur IBM PC/AT et les fabricants

clones ont suivi.

1Rappel historique Bref sur la famille 80x86

Les mP 80386 et 80486

- Les utilisateurs demandent toujours des mP plus puissants. Ainsi Intel introduit en 1985 le mP

80386 (Appelé également 80386DX). Un mP d’architecture 32-bits (interne et externe) et un

bus d’adresses de 32-bits, capable de cibler une mémoire physique de 4Go. Sa mémoire

virtuelle a été augmenté à 64 To.

- Tout les mP précédents sont a utilisation générale, donc ne sont pas capable de traiter

rapidement des opérations mathématiques. Intel a mis sur le marche des circuits co-

processeurs mathématiques, comme les 8087, 80287 et 80387.

- Plus tard Intel a introduit le mP 80386SX, qui a la même architecture interne que le mP 80386

mais avec un bus de données a 16-bits et un un bus d’adresses a 24-bits (1Mo de mémoire).

Ce qui rend son prix moins cher.

-Avec l’introduction du mP 80486, Intel a amélioré le mP 80386 en intégrant un co-processeur

mathématique dans une seule puce. En plus d’autres caractéristiques telles que mémoire

cache (mémoire SRAM a temps d’accès très rapide), ont été introduites.

- Il est important de noter que les programmes écrit pour le mP 8088/86 peuvent être exécutés

également sur les mP 80x86.

-D’autres générations qui sont venus après les mP 80x86 ont pour noms mP Pentium.

2: A l’intérieur du

m

P 8088/8086

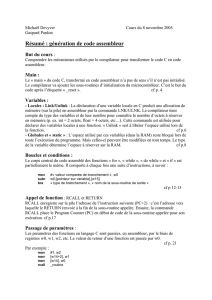

Pipeline

- Avec les mP 8088/86 Intel unités EU et BIU concurrentes (travaillent simultanément).

-BIU la mémoire et les périphériques +EU exécute les instructions recherchées précédemment.

-BIU possède un buffer (chaîne), qui permet de stocker les instructions précédentes:

mP8088 possède une chaîne de 4 octets et le mP8086 en possède 6 octets.

-Si une instruction est lente pour s’exécuter, le buffer se voit remplir vite et y restera ainsi

La BIU ne cherche une nouvelle instruction que s’il y’a 2 octets inoccupés dans le buffer

(mP8086) et 1 octet ( mP8088).

-Pour mP8088/86, il existe 2stages de pipeline: fetch et exécute. Avec les mP plus puissants, il y’a

plusieurs niveaux de pipeline.

-Pipeline + largeur du bus de données conception de puissants mPs.

Fetch 1 Execute 1 Execute 2

Fetch 2

Fetch 1

Fetch 2

Fetch 3

Execute 1

Execute 2

Execute 3

Execution avec

Pipeline

mP 80x86

Execution Sans Pipeline

mP8085

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

1

/

19

100%