ppt, 249KB

Résumé

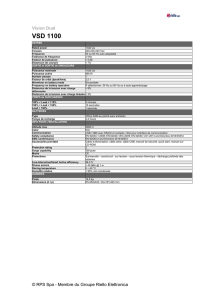

BUS SYSTÈME

Registres

Unité de

Traitement

Unité

Flottante

Unité de

Contrôle

Décodeur

PC

ALU

CPU

MÉMOIRE

PRINCIPALE IO IO IO

Cache

Données

Cache

Instructions

Séquenceur

CK

n BASCULES

Opcode Opérandes

Fanions

RAM

Contrôle

SLC

Opérandes

Instruction

Adresse

CK

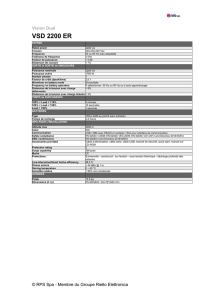

Séquenceur

CK

n BASCULES

Opcode Opérandes

Fanions

RAM

Contrôle

SLC

Opérandes

Instruction

Adresse

CK

Résumé

CK

Offset

SLC

Opcode

Condition

Fanions

+1

Adresse

+

PC

PC+PC+

offset

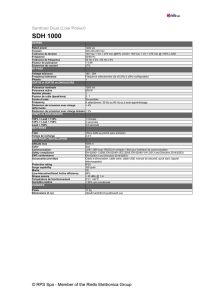

Résumé

Mémoire

Séquenceur

CK

IR

Opcode Opérandes

Fanions

RAM

Contrôle

SLC

Opérandes

MDR MAR

CK

PC

PC+adresse initiale

MAR PC+

MDR M[MAR]

IR+MDR

décodification de IR

PC+PC+1

saut?

contrôle?

adresse?

exécution

chargement

OUI

NONOUI

NONOUI NON

CK

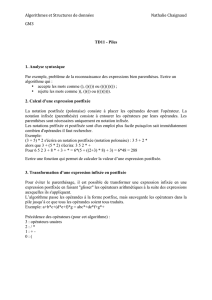

Complication #1

Comment peut fonctionner un processeur 8 ou 16

bits quand les instructions doivent coder tellement

d'informations? ou

Comment réaliser des instructions qui nécessitent

plus d'opérandes que ne peut coder un seul mot

mémoire? ou

Comment exécuter des instructions qui nécessitent

plusieurs coups d'horloge?

Une solution possible: la microprogrammation.

Décodage - Processeurs câblés

Mémoire

Séquenceur

CK

IR

Opcode Opérandes

Fanions

RAM

Contrôle

SLC

Opérandes

MDR MAR

CK

PC

OPCODE O S W

= E E E

ADRESSE N L ALC SHC RRA RRB N WRA

...000 0 0 ØØØ ØØØ ØØØ ØØØ 0 ØØØ

...001 0 1 101 1ØØ ØØØ 000 1 001

...011 0 0 111 1ØØ 000 ØØØ 1 010

...010 0 0 101 1ØØ 000 000 1 011

...100 0 0 001 1ØØ 001 010 1 100

...101 0 0 101 1ØØ 011 100 1 011

...111 1 0 101 1ØØ 011 000 0 ØØØ

...110 0 0 101 010 001 000 1 001

...... .........................

RAM 2NxC

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

1

/

24

100%