Architectures Système sur FPGA Xilinx

Architectures Système sur FPGA

Xilinx

Frédéric LEGER

fleger26@gmail.com

06/11/09

Frédéric LEGER Systèmes sur FPGA Xilinx

2

Sommaire

● Présentation des composants logiques

programmable et leurs applications

● Conception d'une architecture processeur sur

FPGA

● Bases de l'accélération hardware d'un software

● Architectures Linux sur FPGA Xilinx

06/11/09

Frédéric LEGER Systèmes sur FPGA Xilinx

3

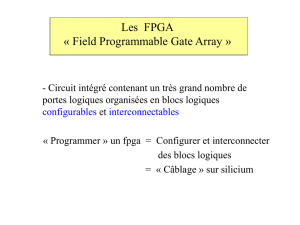

Présentation des composants logiques

programmable et leurs applications

Les composants logiques programmables sont des

circuits composés de nombreuses cellules logiques

élémentaires librement assemblables. Celles-ci sont

connectées de manière définitive ou réversible par

programmation, afin de réaliser la ou les fonctions

numériques voulues.

06/11/09

Frédéric LEGER Systèmes sur FPGA Xilinx

4

Présentation des composants logiques

programmable et leurs applications

Historique

1950 - 1er circuit reconfigurable

«the fuse configurable diode matrix» Harris Semiconductor

1968 - 1er PLA «Read Only Associative Memory», IBM

1983 - 1er GAL effaçable électriquement, Lattice

1984 - 1er FPGA par XILINX (600 portes logiques)

2002 - 1er FPGA intégrant 2 processeurs 32bits câblés, XILINX

2004 - les FPGA investissent l’A380, ACTEL

2006 - 300 millions de portes sur un FPGA, XILINX

2006 aussi.... un AMIGA sur un petit FPGA... le minimig.

2007 - la fréquence des FPGA monte à 600Mhz, ALTERA

06/11/09

Frédéric LEGER Systèmes sur FPGA Xilinx

5

Présentation des composants logiques

programmable et leurs applications

TOPOLOGIE DU FPGA :

Matrice de blocs logiques reliés par un réseau d’interconnexion

programmable complexe

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

1

/

46

100%