Chapitre 7 Conception en Vue du Test : Test Intégré (BIST)

Chapitre 10

Test des Mémoires et des PLAs

« Programmable Logic Array »

Cours ELE6306

Département de Génie Électrique

École Polytechnique de Montréal

1

ELE6306 – Chap. 10 : Test des mémoires © A. Khouas

Plan

)Les circuits à structures régulières

¾Définition

¾Test des circuits à structures régulières

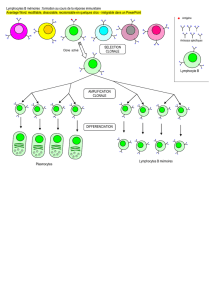

)Test des mémoires

¾Caractéristiques des mémoires

¾Modèles de fautes

¾Algorithmes de test

)Test des PLA « Programmable Logic Array »

¾Caractéristiques des PLAs

¾Modèles de fautes

¾Algorithmes de test

2

ELE6306 – Chap. 10 : Test des mémoires © A. Khouas

Les circuits à structures régulières

)Définition :

¾Ce sont les circuits composés d’une même structure qui se

répète

Les mémoires

Les PLAs « Programmable Logic Array », CPLD, FPGA

Les parties chemins de données dans les microprocesseurs

)Test des circuits à structures régulières :

¾Inefficacité des méthodes générales

Modèles de fautes

Algorithmes de générations

¾Adaptation de la technique de test aux structures des

circuits

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

1

/

51

100%