Cours 2. Inverseur CMOS en mode courant - SoC

university-logo

Logique en mode courant : principes

Transistor MOS

Analyse d’inverseur en mode grand signal

Analyse petit signal

Réalisation de la charge

Fréquence d’oscillations

Polarisation : considérations élémentaires

Cours 2. Inverseur CMOS en mode courant

Dimitri Galayko,

dimitri.galayk[email protected]

LIP6

University of Paris-VI

France

Cours IP-AMS

ACSI M2

Novembre 2009

1/46

university-logo

Logique en mode courant : principes

Transistor MOS

Analyse d’inverseur en mode grand signal

Analyse petit signal

Réalisation de la charge

Fréquence d’oscillations

Polarisation : considérations élémentaires

Outline

1Logique en mode courant : principes

2Transistor MOS

3Analyse d’inverseur en mode grand signal

4Analyse petit signal

5Réalisation de la charge

6Fréquence d’oscillations

7Polarisation : considérations élémentaires

2/46

university-logo

Logique en mode courant : principes

Transistor MOS

Analyse d’inverseur en mode grand signal

Analyse petit signal

Réalisation de la charge

Fréquence d’oscillations

Polarisation : considérations élémentaires

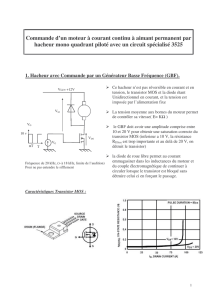

Logique en mode courant

Circuit idéal : inverseur/suiveur

Vdd Vdd Partie droitePartie gauche

V dd C

R

I

t= 0

R

R

V dd C

R

t

”0” ”1”

A t¿0 (apr`es la commutation) :

CC

Vout

Vout

Vout

Vout

Vout

Vout

Vdd

Vdd −RI

La transistion est exponentielle, avec une constante de temps de RC.

3/46

university-logo

Logique en mode courant : principes

Transistor MOS

Analyse d’inverseur en mode grand signal

Analyse petit signal

Réalisation de la charge

Fréquence d’oscillations

Polarisation : considérations élémentaires

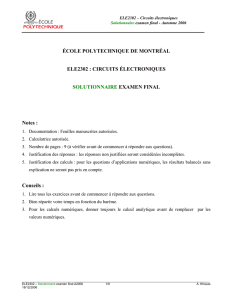

Logique en mode courant

Réalisation pratique

Vdd Partie gauche

NMOS

Vdd

PMOS

Zone ohmique

Zone de saturation

Vdd

R=V n bias

=

Le transistor est ici en r´egime de saturation.

V p bias

V p bias Vin

Vin

V n bias

t

Le transistor est ici en r´egime ohmique.

Vout Vout

Ici le gain diff´erentiel est n´egatif,

d´efinie en cons´equence

la tension de sortie differentielle est

4/46

university-logo

Logique en mode courant : principes

Transistor MOS

Analyse d’inverseur en mode grand signal

Analyse petit signal

Réalisation de la charge

Fréquence d’oscillations

Polarisation : considérations élémentaires

Exemple d’une cellule logique complexe (1)

Arbre de décision pour AB

A

B

01

1

1

0

0

La sortie

5/46

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

1

/

46

100%