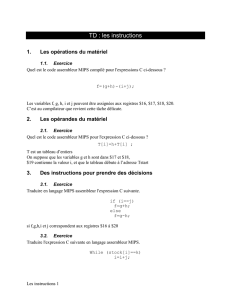

CM2 - assembleur MIPS

CM2

L’architecture MIPS32

Olivier Marchetti (CM-TD-TP) Laurent Lambert (TD-TP)

Laboratoire d’informatique de Paris 6 – Pˆole SoC – UPMC

Ann´ee 2016-2017

Instructions MIPS ?Contrˆole ?Donn´ees en MIPS ?E/S en MIPS

Question du jour : comment programmer un ordinateur ?

Comment parler avec quelqu’un d’aussi binaire qu’un ordinateur ?

Soit en binaire ou alors... avoir un traducteur !

UNIX, l’assembleur et C

IComme tout SE de l’´epoque, UNIX fut ´ecrit en assembleur.

IDennis Ritchie d´eveloppa le C au d´ebut des ann´ees 70.

IUNIX fut r´e´ecrit en C en 1972 !

L’oeuf et la poule

Qui compile le compilateur ? Comment est ´ecrit le compilateur ? Comment concevoir

un langage de haut niveau ? ...

Olivier Marchetti CM2 – L’architecture MIPS32 Ann´ee 2016-2017 2 / 36

Instructions MIPS ?Contrˆole ?Donn´ees en MIPS ?E/S en MIPS

Question du jour : comment programmer un ordinateur ?

Comment ´eviter de programmer en langage machine ?

En utilisant le langage assembleur

de l’architecture.

XPlus aucune variable

=⇒orchestrer un va-et-vient

entre CPU et RAM.

XPlus aucun type

=⇒organiser en m´emoire les

donn´ees.

XPlus aucune structure de

contrˆole ou structure de donn´ees

=⇒les r´einventer en jouant avec

des ´etiquettes assembleurs.

I32 registres utilisateur

de 32 bits chacun.

I232octets adressables.

IDes registres d´edi´es (no-

tamment pour les flot-

tants)

IQuelques conventions

pour la m´emoire.

IEtiquetter des portions

du code assembleur.

IDes instructions de

branchement.

IDes instructions de saut.

Programmer en ensembleur... ou se substituer au compilateur

ISavoir pr´ecis´ement o`u ´ecrire, o`u lire.

ISavoir d´ecomposer tous les traitements.

Olivier Marchetti CM2 – L’architecture MIPS32 Ann´ee 2016-2017 3 / 36

Instructions MIPS ?Contrˆole ?Donn´ees en MIPS ?E/S en MIPS

Pr´esentation du MIPS32 – G´en´eralit´es

MIPS – Microprocessor without Interlocked Pipeline Stages

Architecture ´etudi´ee dans cette UE... made in Stanford !

Architecture

IPremier CPU en 1985.

I32 ou 64 bits.

IArchitecture sous licence...

PS2, PSP, Nintendo,

Jeu d’instructions

IType RISC (Reduced Instruc-

tion Set Computer ).

ITaille fixe pour les instructions.

IPipeline instructions (cf. der-

nier CM).

Facile `a apprendre (r´eguli`ere), suffisamment g´en´eral, int´eressant.

Olivier Marchetti CM2 – L’architecture MIPS32 Ann´ee 2016-2017 4 / 36

Instructions MIPS ?Contrˆole ?Donn´ees en MIPS ?E/S en MIPS Arithm´etiques ?Logiques ?Transfert ?Constantes ?Branchement

Plan

1Instructions MIPS

Instructions arithm´etiques

Instructions logiques

Instructions de transfert de donn´ees

Instructions avec constantes

Instructions de branchement

2Structure de contrˆole en MIPS

Structure de contrˆole if ... then ...

Structure de contrˆole if ... then ... [else]

Structure de contrˆole while

Structure de contrˆole for

3Donn´ees en MIPS

D´eclarer et d´efinir des variables

Convention sur les registres

4Entr´ee/Sortie en MIPS

Olivier Marchetti CM2 – L’architecture MIPS32 Ann´ee 2016-2017 5 / 36

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

1

/

36

100%