Laboratoire #6.pgs

Cours ELE2302 Circuits Électroniques Automne 2005

Cours ELE2302 Circuits Électroniques Page 1 de 8

Laboratoire #6 La logique CMOS 2005/11/20 18:04

Note:: - La feuille de préparation est à la page 8

- La feuille de préparation DOIT être remplie personnellement et remise en entrant

au laboratoire, sans quoi elle ne sera pas corrigée.

CARACTÉRISTIQUES de la logique CMOS

OBJECTIFS:

Le but de ce laboratoire est d'étudier les caractéristiques des portes logique en

technologie CMOS. Plus particulièrement, les niveaux logiques, les marges de bruit, le FAN-

OUT, les caractéristiques AC.

Les paragraphes suivants donnent une description sommaire de la logique CMOS.

1.0 Préparation

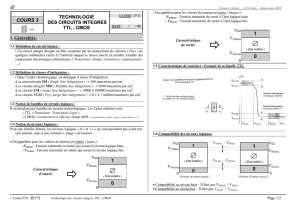

1.1 Circuits internes de la logique CMOS

La figure 1 illustre une porte NOR CMOS typique. Q1 et Q2 sont des transistors MOS à

enrichissement, canal "P", Q3 et Q4 sont des transistors MOS à enrichissement, canal "N". La

plupart des circuits intégrés CMOS ont une tension d'alimentation pouvant varier entre +3V

et +15V selon l'utilisation, (sauf les circuits CMOS à grande vitesse (HC, SC etc.) qui sont

limités à 5 Volts).

La porte de la figure 1 réalise la fonction NOR de la façon suivante: Si les deux

entrées A et B sont à l'état BAS, Q1 et Q2 conduisent, tandis que Q3 et Q4 sont inactifs, la

sortie est alors à l'état HAUT. Si au moins une des deux entrées est à l'état HAUT, Q1 ou Q2 est

inactif, et Q3 ou Q4 conduit, la sortie est alors à l'état BAS . La figure 2 illustre une porte

NAND en CMOS: la position des transistors en série et en parallèle est inversée par rapport

à la porte NOR. La figure 3 représente la porte la plus simple, c'est-à-dire, l'inverseur.

1.1 Consommation

1.1.1 Consommation statique

Figure 1 NOR

Vcc

A

B

Q1

Q2

Q4

Q3

OUT

Figure 2 NAND

Vcc

A

B

Q2

Q

3

Q4

Q1

OUT

Figure 3 Inverseur

IN

Q

1

OUT

Vcc

Q2

Cours ELE2302 Circuits Électroniques Automne 2005

Cours ELE2302 Circuits Électroniques Page 2 de 8

Laboratoire #6 La logique CMOS 2005/11/20 18:04

L'entrée d'un transistor MOS est essentiellement capacitive (environ 7.5pF en parallèle avec

une résistance > 1012 ohm). L'impédance d'entrée d'une porte CMOS est donc très grande.

Une sortie CMOS n'a alors presque pas besoin de fournir du courant à une entrée CMOS et la

chute de tension dans les transistors de sortie est presque nulle. Donc, les niveaux logiques

rencontrés en CMOS sont essentiellement égaux à Vcc (pour le niveau haut), ou à 0 Volt (pour

le niveau bas), du moins en l'absence de charges d'autre nature appliquées à la sortie.

D'autre part, l'examen du circuit montre qu'il n'existe normalement aucun chemin pour le courant

d'alimentation. En effet, dans le cas de la porte “NOR”, si l'un des transistors Q

1

ou Q

2

est éteint,

la combinaison série de ces deux éléments constitue un circuit ouvert, et il ne peut y passer

aucun courant. Dans le cas contraire, si les deux transistors ont allumés, alors les transistors Q

3

et

Q

4

seront tous deux éteints, et le courant n'aura aucun chemin possible vers la masse. Il ne

passera donc aucun courant. La figure 4 illustre tous les cas possibles, en remplaçant, chaque

transistor par une résistance ou un circuit ouvert, suivant l'input. On voit que le courant

d'alimentation est nul dans tous les cas, car il n'y a pas du chemin continu de V

CC

à la masse.

QP1: Montrez que pour le circuit “NAND” de la figure 2, il n'existe aucun chemin pour le

courant d'alimentation (de V

cc

vers la masse) quelle que soit la combinaison de niveaux

hauts et bas appliqués à “A” et “B”.

Il faut noter que ceci ne s'applique que dans des conditions statiques, i.e. quand les

niveaux à l'entrée (et par conséquent à la sortie) ne changent pas et sont carrément hauts (V

CC

)

ou bas (0 volt)

1.1.2 Consommation dynamique.

Si les signaux appliqués à l’entrée d’un circuit CMOS sont carrément hauts ou bas, le

courant d’alimentation est pratiquement nul. Cependant, il se trouve que lors des transitions d’un

Figure 4 Circuits équivalents du NOR suivant ses entrées

10 ou 01

Q2

Vcc

5 volts

0volt

Q1

Q4

Q3

OUT

00

Q1

Q2

Vcc

0volt

0volt

Q4

Q3

OUT

11

Vcc

A

5 volts

Q1

Q2

Q4

Q3

OUT

5 volts

Cours ELE2302 Circuits Électroniques Automne 2005

Cours ELE2302 Circuits Électroniques Page 3 de 8

Laboratoire #6 La logique CMOS 2005/11/20 18:04

état à un autre, la capacité de charge doit être chargée ou déchargée (suivant la direction du

changement). Il en résulte qu’à chaque cycle, une certaine charge est transférée de V

CC

vers la

masse, d’où il résulte un courant moyen beaucoup plus grand que le courant de repos.

QP2 En négligeant tous les autres effets, quel sera le courant moyen d’alimentation d’un

inverseur (figure 3) chargé par un condensateur de 1nF si le circuit est utilisé pour

inverser une onde carrée de 1MHz? (V

CC

=5volts)

1.2 CARACTÉRISTIQUES VIS-À-VIS LE BRUIT

Le comportement des circuits vis-à-vis le bruit

dépend fortement des conditions d'utilisation. En

général, on spécifie deux caractéristiques

intimement liées: l'immunité au bruit et la marge

de bruit.

1.2.1 L'immunité au bruit

C'est une caractéristique propre à chaque

circuit et qui constitue une mesure de la différence

maximale que le circuit peut tolérer de façon

certaine entre le niveau recommandé à son entrée

et le niveau effectivement appliqué. Par exemple,

la tension basse recommandée à l'entrée d'un

circuit TTL est zéro volt, et le manufacturier

garantit que le circuit acceptera comme basse, toute tension inférieure à 0.8 V. Il s'ensuit que

l'on peut dire que l'immunité au bruit à l'entrée d'un circuit TTL à l'état bas est de 0.8 V.

QP3 Si le manufacturier d'un circuit spécifie à 1.5 volts la tension maximale acceptable

comme tension basse à l'entrée d'un circuit, et à 3 volts la tension minimale acceptable

comme tension haute au même endroit, quelle est l'immunité au bruit de ce circuit pour

une entrée basse, et pour une entrée haute?

1.2.2 Marge de bruit

La notion de marge de bruit vient du fait que dans des conditions réelles d'opération, les

tensions appliquées à l'entrée des circuits diffèrent des tensions recommandées, même en

l'absence de bruit. Il en résulte que l'immunité réelle au bruit s'en trouve réduite. C'est cette

immunité restante, constituée par la différence entre le niveau maximal acceptable à l'entrée du

circuit et le niveau effectivement appliqué (en l'absence de bruit), que l'on appelle habituellement

la marge de bruit. Par exemple, pour les circuits TTL encore, les manufacturiers spécifient que

la tension de sortie à l'état bas d'une porte chargée au maximum de courant spécifié dans la

norme (16 mA pour le TTL standard) sera inférieure à 0.4 volt. Puisque l'immunité au bruit à

l'entrée d'une porte TTL est de 0.8 volt à l'état bas, on pourra dire que le circuit jouit d'une

Figure 5 Double inverseur

V

CC

=5volts

200Ω

200Ω

Q

1

OUT

Q2

IN

Q

1

Q2

Cours ELE2302 Circuits Électroniques Automne 2005

Cours ELE2302 Circuits Électroniques Page 4 de 8

Laboratoire #6 La logique CMOS 2005/11/20 18:04

marge de bruit de 0.4 volt à l'état bas, i.e. la différence entre le niveau maximal acceptable

comme niveau bas à l'entrée, et le niveau bas maximal garanti par la sortie à laquelle cette entrée

est connectée.

Il est à remarquer que ces notions sont fortement simplifiées et ne constituent nullement

la totalité de l'information nécessaire pour évaluer la fiabilité éventuelle d'un circuit vis-à-vis le

bruit. L'agencement des circuits, les diverses impédances vues par les sources de bruit, la

rapidité de réponse, la vitesse des transitions des sorties peuvent chacun avoir une influence plus

grande que les valeurs absolues de l'immunité au bruit ou de la marge de bruit.

QP4 Pour le circuit de la figure 5, si le transistor Q1 en conduction a une impédance de 200 Ω

et si le transistor Q2 a une impédance de 100 Ω en conduction, quelle sera la marge de

bruit à l'entrée du deuxième inverseur quand l'entrée du premier inverseur est basse, et

quand elle est haute?

Note: Les deux résistances représentent le circuit équivalent d'une charge non-spécifiée qui

serait connectée à la sortie du premier inverseur, qui est aussi l'entrée du second. Pour

résoudre le problème, il faut, pour chaque cas de l'entrée du premier inverseur (haute ou

basse), représenter la sortie de ce dernier par son circuit équivalent de Thévenin, et

calculer la tension qui sera alors appliquée à l'entrée du second inverseur.

1.3 "FAN-OUT" (certains parlent de "Sortance")

Il est convenu d'appeler "FAN-OUT" ou “sortance” le nombre d'entrées de portes

qu'une sortie peut entraîner. Ceci est encore une notion simplifiée qu'il convient de qualifier.

Par exemple, on spécifie habituellement que le "FAN-OUT" d'une porte TTL standard

alimentant d'autres portes TTL standard est de 10. Cependant, si l'on désire augmenter la marge

de bruit (à cause des conditions ambiantes) ou si au contraire on peut se permettre une marge de

bruit réduite, cette spécification devra ou pourra être réajustée.

1.3.1 “FAN-OUT” statique.

Comme une entrée CMOS n'a presqu'aucune exigence de courant, il semblerait que le

FAN-OUT d'une porte CMOS alimentant d'autres portes CMOS soit essentiellement

infini.

1.3.2 “FAN-OUT” dynamique.

Ce serait trop beau, il n'en est habituellement rien. En effet, lors des transitions, la sortie

d'une porte doit fournir le courant requis pour charger la capacité d'entrée des portes qui y

sont connectées. Puisque d'une part, l'impédance de sortie n'est pas nulle, et que d'autre

part, le courant ainsi produit doit circuler dans des conducteurs extérieurs au circuit, et

qui présentent nécessairement des caractéristiques inductives, capacitives et résistives, il

est facile de prévoir que toute augmentation du “FAN-OUT” imposé à un circuit réduira

sa vitesse. La responsabilité de déterminer le “FAN-OUT” acceptable dans une condition

donnée, revient donc au concepteur. En simplifiant, un grand “FAN-OUT” signifie une

grande charge capacitive sur le circuit. Lors du passage de l'état haut (nominalement

Cours ELE2302 Circuits Électroniques Automne 2005

Cours ELE2302 Circuits Électroniques Page 5 de 8

Laboratoire #6 La logique CMOS 2005/11/20 18:04

V

OH

=V

CC

) à l'état bas (nominalement V

OL

=0 volt), le condensateur est initialement

chargé, et on vient placer la résistance équivalente d'un transistor (Q

2

dans le cas de

l'inverseur de la figure 3) à ses bornes. Le circuit de la figure 6, ci-contre, montre ce qui

se passe lors d'un changement d'état de l'entrée. Le

commutateur est dans la position haute si l'entrée est basse, et

dans la position basse si l'entrée est haute. Les deux résistances

représentent respectivement les impédances des deux

transistors quand ceux-ci sont allumés. Il est clair que le temps

de décharge (ou de descente) dépend de la valeur du

condensateur de charge (C

L

). Pour la transition inverse, le

condensateur est initialement déchargé, et on vient le relier à

V

CC

à l'aide de la résistance du transistor Q

1

.

QP5 Avec les impédances des transistors données plus haut, quelles

seront les temps de montée (0% à 90%) et de descente (100% à

10%) à la sortie de l'inverseur de la figure 3 s'il est connecté à une charge capacitive de

1nF?

Note: Cette capacité est fortement exagérée, pour faciliter les mesures au laboratoire. En fait,

dans le cas habituel, la capacité de charge dépassera rarement 75pF, soit l'équivalent

d'environ dix (10) entrées de portes CMOS.

QP6 Quelle est la capacité de charge la plus grande qui permette encore d'espérer des temps de

montée et de descente inférieurs à 20nS?

Note: On peut considérer ici que les transistors commutent de façon instantanée car leurs temps

d'allumage et d'extinction sont négligeables devant l'effet de cette charge capacitive.

1.4 Caractéristiques de transfert du CMOS

En temps normal, les signaux appliqués à l'entrée d'un circuit CMOS sont carrément

hauts ou bas. Cependant, il arrive que les transitions d'un état à un autre se fassent lentement

(cas, par exemple, d'une charge capacitive), et cela peut affecter les performances de plusieurs

façons. Lorsque l'entrée n'est ni vraiment haute ni vraiment basse, les deux transistors (Q

1

et Q

2

,

figure 3) sont partiellement allumés. Il en résulte que le courant d'alimentation augmente

considérablement, pour la porte concernée. De plus, la tension de sortie risque alors de n'être ni

haute ni basse, ce qui affectera les portes dont les entrées sont connectées à cette sortie et ainsi

de suite.

En général, si les transitions à l'entrée d'un circuit sont lentes, les effets seront de quatre

classes principales.

- Ralentissement des transitoires à la sortie. En général, elles seront tout-de-même plus

rapides qu'à l'entrée.

- Pertes de synchronisme. Si un signal avec un temps de transition trop lent est appliqué

sur les entrées de plusieurs portes, les différences entre les niveaux critiques de ces portes

entraîneront des différences entre les moments où elles commuteront.

- Pertes de stabilité. Les circuits peuvent osciller si leurs entrées demeurent trop longtemps

Figure 6, Inverseur

Circuit Thévenin

V

CC

=5volts

200Ω

Q

1

OUT

Q2

100ΩC

L

IN=L

IN=H

6

6

7

7

8

8

1

/

8

100%