Les circuits logiques2 [Mode de compatibilité]

Chapitre 3 : Circuits Logiques

Chapitre 3 : Circuits Logiques

E1

Le multiplexeur (N vers 1):

Un multiplexeur est un circuit logique à N entrées dites de données (ou d’informations) et une sortie

qui transmet les informations parvenant à l’entrée sélectionnée. La sélection d’une entrée s’effectue

par le mot binaire N provenant des n entrées d’adresse. Ces entrées d’adresse (mot de commande ou

d’adresse) codent le n°de l’entrée de données. Les nombres n et N sont liés par la relation : N = 2n.

L’expression de S est pour un multiplexeur 4 vers 1 :

E

E1

E2

En

E3 S

b0 b1 b2 ... bM

Mot de commande

Xn-1 ….X0

L’expression de S est pour un multiplexeur 4 vers 1 :

(

)

( ) ( ) ( )

( )

013012011010

321001

,,,,,

XXEXXEXXEXXE

EEEEXXS

+++ =

X0

X1

0 1

0

1

E0E1

E2E3

E

0

E1

E2

EN-1

Chapitre 3 : Circuits Logiques

E0

E1

E

S

E

2

E3

GX0X1

Chapitre 3 : Circuits Logiques

Exemple : 74LS151

Ce circuit référencé 74LS151 est appelé

sélecteur/multiplexeur 8 vers 1

c’est à dire

qu’il possède 8 entrées de données (D0 à D7) pouvant être aiguillé vers la sortie Y

(ou Y=W) grâce aux entrées de commande A, B et C.

La validité du circuit se fait par l’entrée de sélection (chip select) notée G.

(voir Mémotech électronique, p99)

G

A

B

C

G 0/7

MUX

Y

D0

D1

D2

D3

D4

D5

D6

D7

0

1

2

3

4

5

6

7

8

Inhibition

Entrées de

Données

Mot de

Commande

0

2

EN

W

G C B A Y W

H X X X B H

B B B B D0D0

B B B H D1D1

B B H B D2D2

B B H H D3D3

B H B B D4D4

B H B H D5D5

B H H B D6D6

B H H H D7D7

Chapitre 3 : Circuits Logiques

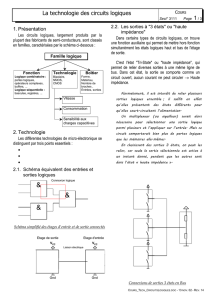

Complément sur la norme IEEE/ANSI :

G

MUX

Inhibition

EN

Le libellé signifie une dépendance fonctionnelle de type ET avec les entrées de

sélection et chacune des entrées de données de 0 à 7.

0

7

G

G

A

B

C

G 0/7

MUX

Y

D0

D1

D2

D3

D4

D5

D6

D7

0

1

2

3

4

5

6

7

8

Entrées de

Données

Mot de

Commande

0

2

W

}

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

1

/

49

100%