T - Ummto

REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE

MINISTERE DE L’ENSEIGNEMENT SUPERIEUR ET DE LA RECHERCHE SCIENTIFIQUE

Université MOULOUD MAMMERI de TIZI-OUZOU

Faculté de génie électrique et d’informatique

Département d’Electronique

Mémoire de Magister en Electronique

Option : Microélectronique

Présenté par :

Mr KACI Yahia

Thème

Soutenue le 15 Janvier 2015 devant le Jury :

Mr MEGHERBI Mohamed : Professeur Président, UMMTO.

Mr BELKAID Mohamed Saïd : Professeur Directeur de mémoire, UMMTO.

Mr HAMICHE Hamid : Maître de conférences A Examinateur, UMMTO.

Mr MELLAH Rabah : Maître de conférences A Examinateur, UMMTO.

Mr ZIRMI Rachid : Maître de conférences B Examinateur, UMMTO.

Etude d’une nouvelle approche MLI (PWM) en temps réel basée

sur le principe des réseaux de neurones destinée aux véhicules

électriques

Remerciement

Je remercie le Bon Dieu de m’avoir donné la volonté et la patience qui m'ont permis de

mener à bien ce travail.

Je remercie vivement mon Promoteur, Monsieur M.S.BELKAID, Professeur à

l’université Mouloud Mammeri de Tizi-Ouzou pour son suivi, son aide documentaire et son

soutien matériel précieux, je voudrais aussi remercier Monsieur A. GUELLAL chercheur au

niveau de laboratoire de l’équipe économie et maîtrise d’énergie au Centre de Recherche des

Energies Renouvelables (CDER) de Bouzaréa pour son aide précieuse, son soutien durant la

préparation de ce travail.

Je tiens à adresser mes sincères remerciements à tous les membres de jury qui ont

accepté de juger ce travail et d’y apporter leur caution chargé d’examiner la soutenance de

mon projet de magister.

Je voudrai exprimer mon profond respect à tous les Enseignants qui m’ont encadré

durant mon étude.

Je ne saurai oublier de remercier toute personne qui, d’une manière ou d’une autre, m’a

aidé dans l’élaboration de ce travail.

Dédicace

Je dédie ce travail à :

Mes parents,

Mes frères et mes soeurs,

Toute ma famille,

Ainsi qu’à tous mes amis.

Sommaire

Sommaire

Liste des tableaux………………………………………………………………………………

Liste des figures………………………………………………………………………………...

Liste des acronymes et nomenclatures……………………………………………………….

Introduction générale…………………………………………………………………........... 1

Chapitre 1. Machines asynchrones et onduleurs de tension……………………………… 3

1. Véhicule électriques…………………………………………………………………....... 3

2. La machine asynchrone (MAS)……………………………………………………........ 4

2.1. Introduction………………………………………………………………………. 4

2.2. Constitution et principe de fonctionnement…………………………………….. 4

2.3. Modélisation de la machine asynchrone……………………………….............. 4

2.3.1 Equations électriques…………………………………….…..…....……... 5

2.3.2 Equations magnétiques …………………………………………………. 6

3. Commande des moteurs asynchrones…………………………………....................... 7

3.1. Introduction………………………………………………………………………. 7

3.2. Commande scalaire………………………………………………....................... 7

3.2.1. Contrôle en V/f de la machine asynchrone…………….......................... 7

3.2.2. Contrôle scalaire du courant………………………............................... 8

3.3. Commande vectorielle………………………………………….…...……………. 8

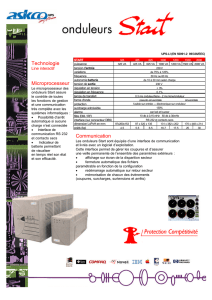

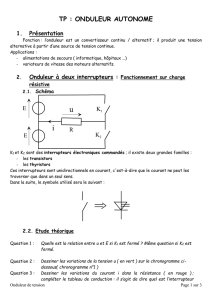

4. Onduleur de tension………………………………………………….………………… 8

4.1. Définition et principe…………………………………………………………… 8

4.2. Types d’onduleurs……………………………………………………………….. 9

4.2.1. Les Onduleurs monophasés de tension………………………………… 9

4.2.2. Les onduleurs triphasés………………………………………………… 9

4.2.3. Onduleurs multi-niveaux…………………………………...................... 10

4.2.3.1. Onduleur de tension à diode de bouclage (structure NPC)............. 10

Sommaire

4.2.3.2. Onduleur de tension à condensateur flotteur……………………… 11

4.2.3.3. Onduleur de tension en cascade (topologie en H)…………........... 12

5. Types de commande des onduleurs……………………………………………………. 14

a. Stratégie de modulation Tout ou rien………………………………………. 14

b. Stratégie de modulation à pleine onde……………………………………… 14

c. Stratégie de modulation à largeur d’impulsion MLI……………………….. 14

d. Stratégie de modulation Sigma-Delta……………………………………….. 14

5.1. Modulation à largeur d’impulsion MLI………………………………………….. 14

a. MLI intersective (Modulation par porteuse)………………........................ 15

b. MLI Vectorielle (Modulation poste calculer)………………………………. 15

c. MLI pré-calculée (Modulationpré-calcul)………………………………….. 15

Conclusion……………………………………………………………………………… 16

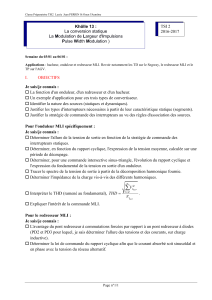

Chapitre 2. Commande d’un Onduleur Triphasé piloté par MLI à Structure

NPC Multiniveaux…………………………………………………………………………….. 17

Introduction……………………………………………………………………………………. 17

1. Modélisation de l’onduleur à cinq niveaux à structure NPC…………………………. 17

1.1. Structure générale de l’onduleur à cinq niveaux…………………………............ 17

1.2. Modélisation du fonctionnement de l’onduleur à cinq niveaux…………………. 18

1.2.1. Différentes configurations d’un bras d’onduleur à cinq niveaux………. 18

2. Commande de l’onduleur triphasé à cinq niveaux à structure NPC……………….. 21

2.1. La technique de PATEL et HOFT……………………………………………….. 25

2.2. Calcul des angles de commutation…………………………………….…........... 26

2.3. Interprétation des graphes……………………………………………………….. 29

3. Simulation de l’onduleur triphasé cinq niveaux……………………………………… 29

3.1.Schéma block…………………………………………………………………........ 29

3.2. Distorsion d’harmonique total THD……………………………………………. 31

3.3. Résultat de simulation……………………………………………………............ 32

3.4. Interprétation des courbes……………………………………………...….......... 35

Conclusion…………………………………………………………………………….............. 36

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

81

81

82

82

83

83

84

84

85

85

86

86

87

87

88

88

89

89

90

90

91

91

92

92

93

93

94

94

95

95

96

96

97

97

98

98

99

99

100

100

101

101

102

102

103

103

104

104

105

105

106

106

107

107

1

/

107

100%