docteur de l`université de bordeaux

THÈSE PRÉSENTÉE

POUR OBTENIR LE GRADE DE

DOCTEUR DE

L’UNIVERSITÉ DE BORDEAUX

ÉCOLE DOCTORALE DES SCIENCES PHYSIQUES ET DE l’INGÉNIEUR

SPÉCIALITÉ : ÉLECTRONIQUE

Par Ala AYED

DÉVELOPPEMENT DE MÉTHODOLOGIES POUR

L’EXTRACTION ET LA CONSTRUCTION DE

MACROMODÈLES D’IMMUNITÉ ÉLECTROMAGNÉTIQUE

APPLIQUÉS AUX CIRCUITS INTÉGRÉS

Sous la direction de : Geneviève DUCHAMP

(Co-encadrants : Tristan DUBOIS & Jean-Luc LEVANT)

Soutenue le 19 décembre 2014

Membres du jury:

M. CAZARRÉ, Alain

Professeur, Université Paul Sabatier

Président

Mme. DUCHAMP, Geneviève

Professeur, Université de Bordeaux

Directrice de thèse

M. DUBOIS, Tristan

Maître de conférences, Université de Bordeaux

Co-encadrant

M. LEVANT, Jean-Luc

Docteur ingénieur, Expert CEM, ATMEL, Nantes

Co-encadrant

M. PERDRIAU, Richard

Enseignant Chercheur-HDR, ESEO

Rapporteur

M. VOLLAIRE, Christian

Professeur, Ecole Centrale de Lyon

Rapporteur

Mme. FRÉMONT, Hélène

Maître de conférences-HDR, U. de Bordeaux

Examinateur

TABLE DES MATIÈRES

Introduction générale ............................................................................................................... 1

Chapitre 1 : Généralités sur la compatibilité électromagnétique & CEM des circuits

intégrés ...................................................................................................................................... 4

1. Généralités sur la compatibilité électromagnétique .......................................................... 5

1.1. Introduction ..................................................................................................................... 5

1.2. Niveaux de compatibilité ................................................................................................. 7

1.3. Sources des perturbations électromagnétiques ................................................................ 7

1.3.1. Classification des sources ......................................................................................... 7

1.3.2. Exemples de sources de perturbation ........................................................................ 8

i) Décharges électrostatiques .......................................................................................... 8

ii) Radars ......................................................................................................................... 9

iii) Communications sans fil ............................................................................................ 9

iv) Circuits intégrés ....................................................................................................... 10

1.4. Couplage des perturbations électromagnétiques ........................................................... 10

1.4.1. Couplage rayonné ................................................................................................... 11

1.4.2. Couplage conduit .................................................................................................... 12

2. Compatibilité électromagnétique des circuits intégrés ................................................... 13

2.1. Historique de la CEM des circuits intégrés ................................................................... 14

2.2 Evolution des technologies des circuits intégrés et contraintes CEM ............................ 14

2.3. Emissivité des circuits intégrés ...................................................................................... 19

2.4. Immunité des circuits intégrés ....................................................................................... 20

2.4.1. Effet sur les circuits analogiques ............................................................................ 20

2.4.2. Effet sur les circuits numériques ............................................................................. 21

2.4.3. Effet sur les circuits mixtes ..................................................................................... 22

Conclusion ............................................................................................................................... 23

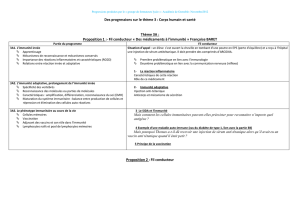

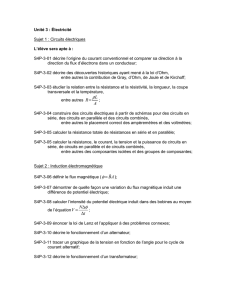

Chapitre 2 : Susceptibilité conduite des circuits intégrés ................................................... 24

Introduction ............................................................................................................................ 25

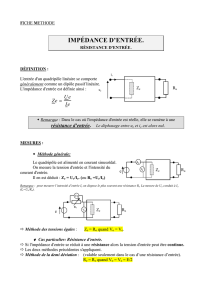

1. Critère de susceptibilité ..................................................................................................... 25

2. Techniques de mesure de la susceptibilité conduite ........................................................ 26

2.1. Injection directe de la puissance (DPI) .......................................................................... 26

2.2. Injection par boucle de courant (BCI) ........................................................................... 27

2.3. Test en cage de Faraday (WBFC) .................................................................................. 28

itoires ........................................................... 29

2.5. Mesure par sonde HFPI ................................................................................................. 30

2.6. Mesure par sonde RFIP ................................................................................................. 31

3. Modélisation de la susceptibilité ....................................................................................... 32

....................................................... 33

3.2. Techniques de modélisation du couplage ...................................................................... 34

..................................................................... 35

3.3.1. Modèle IBIS ............................................................................................................ 35

3.3.2. Modèle IMIC .......................................................................................................... 36

3.3.3. Modèle ICIM-CI ..................................................................................................... 37

Conclusion ............................................................................................................................... 38

Chapitre 3 : Méthode RFIP : Caractérisation de la sonde utilisée et du banc de mesure ..... 39

Introduction ............................................................................................................................ 40

1. Présentation de la technique RFIP ................................................................................... 40

1.1. Principe de la mesure ..................................................................................................... 40

1.2. E .......................................................................... 42

............ 44

2. Etude et caractérisation de la sonde RFIP ....................................................................... 46

2.1. Cahier des charges de la sonde RFIP ............................................................................. 47

2.2. Conception des blocs amplificateurs de la sonde RFIP ................................................. 47

2.3. Etude et caractérisation des blocs amplificateurs .......................................................... 49

2.3.1. Mesure des paramètres S des blocs amplificateurs ................................................. 49

2.3.2. Paramètres S mesurés ............................................................................................. 49

2.4. Choix de la valeur de Zp ................................................................................................ 51

............................................ 53

2.5.1. Limitation fréquentielle et amélioration de la précision de calcul .......................... 53

i. Importance du de-embedding lors de la caractérisation de la sonde RFIP

ii. Techniques de de-embedding utilisées ................................................................... 54

a- Méthode de de-embedding 1 ....................................................................................................... 55

b- Méthode de de-embedding 2 ....................................................................................................... 55

2.5.2. Limitation en puissance injectée ............................................................................. 56

i. Limite avec la configuration actuelle ......................................................................... 56

ii ........ 58

iii. Amélioration de la limite en puissance .................................................................. 61

3. Caractérisation du banc de mesure RFIP ........................................................................ 63

3.1. Caractérisation de la sonde RFIP ................................................................................... 64

3.1.1. Caractérisation des amplificateurs .......................................................................... 65

p .......................................................................... 67

3.2. Caractérisation des éléments du banc de mesure ........................................................... 68

.................................................... 68

3.2.2. Choix et caractérisation du té de polarisation ......................................................... 69

........................................................................ 71

4. Validation de la technique RFIP par mesure sur des composants connus ................... 73

5. Sources des incertitudes de la mesure RFIP .................................................................... 75

Conclusion ............................................................................................................................... 77

Chapitre 4 : Caractérisation et modélisation de l’immunité d’un convertisseur

analogique-numérique ........................................................................................................... 78

1. Présentation du convertisseur analogique-numérique ................................................... 79

1.1. Choix et description du circuit ....................................................................................... 79

1.2. Carte de test ................................................................................................................... 80

1.3. Configurations de mesure et chemins de couplage ....................................................... 81

1.4. Choix du critère de susceptibilité .................................................................................. 82

2. Caractérisation de l’immunité de l’ADC par la technique RFIP .................................. 83

2.2. Validation de la technique RFIP .................................................................................... 84

2.3. Investigation des spécificités des mesures RFIP ........................................................... 85

2.3.1 Courbes de susceptibilité RFIP ................................................................................ 86

................................ 89

3. Analyse de l’immunité du convertisseur analogique-numérique .................................. 90

3.1. Introduction ................................................................................................................... 90

3.2. Dispersion des résultats de conversion et variation de moyenne ...................................... 91

3.3. Hypothèses sur les causes de la dispersion et de la variation de moyenne ................... 92

3.4. Effet des perturbations sur la tension Vin....................................................................... 93

3.5. Effet des perturbations sur la tension VREF .................................................................... 95

3.5.1. Effet des perturbations dans le cas VREF externe .................................................... 96

3.5.2. Effet des perturbations dans le cas VREFinterne ...................................................... 97

4.1. Présentation du modèle ICIM-CI ................................................................................ 100

4.2. Méthodologie de construction du modèle ICIM- .................................... 100

4.2.1. Bloc PDN .............................................................................................................. 100

4.2.2. Bloc IB .................................................................................................................. 101

4.2.3. Fonctionnement du modèle ................................................................................... 103

4.3. Calcul des paramètres du modèle ICIM-CI ................................................................. 104

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

81

81

82

82

83

83

84

84

85

85

86

86

87

87

88

88

89

89

90

90

91

91

92

92

93

93

94

94

95

95

96

96

97

97

98

98

99

99

100

100

101

101

102

102

103

103

104

104

105

105

106

106

107

107

108

108

109

109

110

110

111

111

112

112

113

113

114

114

115

115

116

116

117

117

118

118

119

119

120

120

121

121

122

122

123

123

124

124

125

125

126

126

127

127

128

128

129

129

130

130

131

131

132

132

133

133

134

134

135

135

136

136

137

137

138

138

139

139

140

140

141

141

142

142

143

143

144

144

1

/

144

100%