Les montages de base en microélectronique

L

Le

es

s

b

bl

lo

oc

cs

s

d

de

e

b

ba

as

se

e

p

po

ou

ur

r

l

la

a

c

co

on

nc

ce

ep

pt

ti

io

on

n

d

de

es

s

c

ci

ir

rc

cu

ui

it

ts

s

i

in

nt

té

ég

gr

ré

és

s

Ivan Thomas - mars 2006

I. Rappels sur le transistor en technologie silicium

Les transistors MOS et bipolaires : équations et modèles

II. Les sources de courant et de tension

Sources de courant à transistors bipolaires

Amélioration des sources de courant bipolaires

Sources de courant et tension à transistors MOS

Sources de courant indépendantes de la tension d’alimentation

Sources de courant compensées en température

III. Les montages amplificateurs de base

Amplificateurs à un étage

Amplificateurs de base à transistors bipolaires

Amplificateurs de base à transistors MOS

Tableau récapitulatif

IV. Les amplificateurs différentiels

Amplificateurs différentiels à transistors bipolaires

Amplificateurs différentiels à transistors MOS

Réponse en fréquence des amplificateurs différentiels

Amplificateurs différentiels alimentés par miroir de courant

V. Les amplificateurs à plusieurs étages

Les blocs de base pour la conception des circuits intégrés

Ivan THOMAS 2005-2006 2 /60 Polytech Orléans

I. Rappels sur le transistor en technologie silicium

Les transistors MOS et bipolaires : équations et modèles

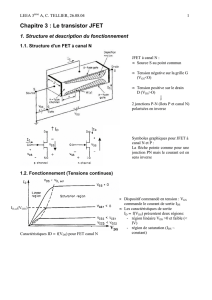

I.1. Le transistor MOS (Metal Oxyde Semi-conducteur)

Transistor MOS canal n à enrichissement

Source et drain sont symétriques.

G est la grille.

• VGS = 0 : les deux jonctions PN Substrat-S et Substrat-D empèchent tout passage de

courant entre S et D → résistance

Ω

12

10

• VGS > 0 : création d’une zone de déplétion de type N sous la grille

• VGS atteint VT (tension de seuil) : apparition du phénomène d’inversion ;

l’augmentation de VGS ne modifie plus la zone de déplétion mais crée une couche

d’électrons (canal N continu) directement sous la grille.

• VGS > VT et VDS > 0 : existence d’un courant d’électrons dans le canal de S vers D.

NB : le substrat est relié au potentiel la plus négatif, sinon possibilité d’utilisation comme seconde ″grille″.

L est la longueur de canal (entre S et D) et W la largeur de canal (dimension orthogonale).

t

ox

Grille n++ polysilicium

Oxyde de grille (SiO2)

Drain (diffusion n+) Source (diffusion n+)

n+

n+

Substrat type p

Substrat (VSS)

L

100

200

300

400

500

600

1 2 3 4

V

DS

(V)

0

IDn (µA) VGS = 3,5V

VGS = 3V

VGS = 2,5V

VGS = 2V

VGS = 1,5V

Zone triode

Zone de saturation

VDS = VGS -V

Tn

5

D

G

S

B G

S

DD

S

B

G

VGS VDS

IDn

VGS

VDS

ID

VB

p

incement

Les blocs de base pour la conception des circuits intégrés

Ivan THOMAS 2005-2006 3 /60 Polytech Orléans

Constatations :

Si VGS < VTn IDn = 0 => zone de cutoff, drain et source restent isolés, il n’y a pas

de conduction.

1) et 2) Si VDS < VGS – VTn => zone où le courant drain IDn dépend de VGS et de VDS. C’est la

zone triode.

4) Si VDS > VGS – VTn le courant drain est indépendant de VDS. C’est la zone de

saturation, à courant constant.

Les équations de courant en régime statique (grands signaux)

W VDS

Dans la zone triode : ID = µn Cox [(VGS – VTn) - ] VDS avec VGS – VDS > VTn

L 2

Xd

B

n+ n+

n+ n+

n+ n+

S

G

D

S

G

D

B

B

y

x QNcharge de

canal

VGS > VTn et VDS très petit :

début de la zone triode

QN constant le long de L

L

QN (y)

QN (y) QN (y=L) = 0

VGS - VDS> VTn

zone triode

QN fonction de y

VDS = VGS - VTn = VDS sat

p

incement

QN fonction de y et QN(y=L) = 0

grille polys. n+

métal

ox

y

de

n+ n+

S

G

D

B

QN (y) QN (y=Leff) = 0

VDS > VGS - VTn = VDS sat

zone de saturation

QN fonction de y et QN(y=L) = 0

S

G

D

1)

2)

3)

4)

Leff = L-Xd

Les blocs de base pour la conception des circuits intégrés

Ivan THOMAS 2005-2006 4 /60 Polytech Orléans

Dans la zone de saturation :

W

ID = µn Cox (VGS – VTn)² (1 + λn VDS) avec VDS ≥ VDsat

2L

Dans les deux équations le terme µn Cox dépend du process.

λn est le paramètre de modulation de longueur de canal et vaut ~ 0,1.L avec λn en V-1 et L en µm

Transistor MOS canal n à dépeuplement (dépletion) :

Un canal N existe sous la grille et ce transistor conduit quand VGS > 0.

Si VGS < 0 , la grille polarisée négativement repousse les charges du canal n qui finit par

disparaître.

Ce transistor est peu utilisé.

Transistor MOS canal P

n+ n+

g

rille n+

p

ol

y

ox

y

de

Canal N préformé par

implantation ionique

S

G

D

50

100

250

300

350

400

1 2 3 4

V

SD

(V)

0

-IDp (µA) VSG = 1,5V

VSG = 1V

VSG = 0,5V

VSG = 0V

VSG = -0,5V

Zone triode

Zone de saturation

5

VG

VD

VSD

G

S

B

D

G

S

D D

Les blocs de base pour la conception des circuits intégrés

Ivan THOMAS 2005-2006 5 /60 Polytech Orléans

Paramètres des transistors MOS :

Dans la zone triode : W VDS

ID = µ Cox [(VGS – VT) - ] VDS

L 2 εox ε0

Cox est la densité de capacité (F/unité de surface) d’oxyde de grille Cox =

tox

µ est la mobilité des porteurs dans le canal (en cm²/V*s).

VT est la tension de seuil.

VT = VT0 ± γ [ √(Φ ± VBS ) - √ Φ ]

Φ est le potentiel de forte inversion en surface

γ est le paramètre de seuil de substrat, dépend du dopage sous la grille

VT0 est la tension de seuil pour VBS = 0 > 0 pour un NMOS à enrichissement

< 0 pour un NMOS à dépeuplement

< 0 pour un PMOS à enrichissement

> 0 pour un PMOS à dépeuplement

√ (2 q Na εs ε0) Na

γ = et = - UT log

Cox ni

Dans la zone de saturation :

Modulation de longueur de canal : λ

()

[]

φ

εε

λ

+−−

=

TGSDS

a

s

VVVL

Nq

.2

.

..2

0

Effet de canal court :

Le champ électrique tangentiel E devient important sous VDS

Augmentation du taux de collisions et saturation de la vitesse des porteurs à partir de Ec

avec Ec champ critique ~ 1,5 106 V/m

v = µn . E vitesse des porteurs

La loi quadratique du courant dans la zone de saturation devient une loi linéaire :

ID

VDS

Idéal : λ=0

1/λ

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

1

/

60

100%