Document

Travaux pratiques – Etude d’un amplificateur MOS source commune

www.emse.fr/~dutertre/enseignement.html - 2015 1

Travaux pratiques – Etude d’un amplificateur source commune.

L’objet de ce TP est de familiariser les étudiants avec la polarisation et l’étude dynamique des

transistors MOS (ici NMOS) lorsqu’ils sont utilisés en amplification.

1. Schéma étudié.

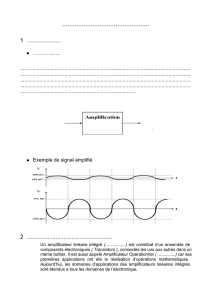

Le circuit étudié, présenté figure 1, est un amplificateur source commune à un transistor : un

NMOS de type VN2222. Il s’agit d’un circuit à éléments discrets (par opposition aux circuits

intégrés). La finalité de ce montage est pédagogique, un circuit réel aurait très probablement

une architecture différente. En particulier, la polarisation est réalisée avec une 2ème source de

tension VPOL, en plus de la polarisation principale VDD, dans un but de manipulation pratique.

Fig. 1 – Amplificateur source commune MOS.

Liste des composants :

- VN2222, transistor NMOS discret,

- RD=1 kΩ, résistance de drain,

- RPOL=10 kΩ, résistance de polarisation,

- Cliaison=2,2 µF, capacité de liaison (attention à ne pas choisir une capacité

électrolytique).

On prendra VDD=10 V.

Les alimentations VDD et VPOL seront fournies par les alimentations stabilisées des établis.

Réalisation du montage :

Le montage sera réalisé sur plaque d’essais. Vous vous attacherez à réaliser un montage

soigné respectant un code couleur pour la clarté (le code couleur des figures 2, 3 et 4 n’est pas

forcement cohérent). La figure 2 propose une schématique du montage sur plaque d’essais. La

photographie correspondante est donnée figure 3.

RD#

RPOL#

VDD#

D

S

G

Cliaison#

VPOL#

Vin#

Vout#

gnd$

VDS#

IDS#

Travaux pratiques – Etude d’un amplificateur MOS source commune

www.emse.fr/~dutertre/enseignement.html - 2015 2

Fig. 2 – Implantation de l’amplificateur source commune sur plaque d’essais.

Fig. 3 – Montage amplificateur source commune (plaque d’essais).

Fig. 4 – Connexion de l’alimentation et des appareils de mesure.

D

G

S

RD%

VDD%

RPOL%

VPOL%

Vout%

Cdec%

Vin%

gnd%

Segment'

conducteur'

Fil'

Connexion'

segment3fil'

.

Alimentation

Alim1

(0-20V)

Alim 2

(0-20V)

Alim 2

Ampère

mètre

.

Volt

mètre

VDD VPOL Vout

gnd

Plaque d’essais

+ +

- -

Travaux pratiques – Etude d’un amplificateur MOS source commune

www.emse.fr/~dutertre/enseignement.html - 2015 3

Compte-rendu :

Vous rédigerez un compte-rendu manuscrit qui sera ramassé en fin de séance.

1.1. Justifier le choix de Cliaison (valeur et technologie de la capacité).

1.2. Quelles sont les grandeurs caractéristiques du NMOS qui vont pouvoir être mesurées

au moyen de l’ampèremètre et du voltmètre ?

2. Polarisation (DC) du montage.

On souhaite polariser le montage de telle sorte que Vout=VDS=VDD/2.

Compte-rendu :

2.1. Calculer la valeur de IDS correspondante.

2.2. Pour quelle valeur de VPOL (obtenue expérimentalement) obtient-on cette

polarisation ? Quelle est la relation liant VPOL et VGS ?

3. Tracer des caractéristiques courant -tension.

Compte-rendu :

3.1. Tracer sur le papier millimétré joint la caractéristique IDS=f(VDS) du transistor pour la

valeur de VGS déterminée au 2. (vous tracerez la caractéristique pour VDS : 0 – 9V, on

pourra faire varier VDD).

3.2. En déduire r0 l’impédance de sortie du NMOS au point de polarisation.

3.3. En déduire également le rDS, on du NMOS (zone linéaire du régime triode). Comparer

la valeur obtenue à la notice du composant.

3.4. Tracer sur le papier millimétré joint la caractéristique IDS=f(VGS) du transistor pour

VDS = 5 V = cte (faire varier VDD pour pouvoir respecter cette contrainte).

3.5. En déduire gm la transconductance du NMOS au point de polarisation.

3.6. En déduire le gain en tension petits signaux de l’amplificateur source commune.

Travaux pratiques – Etude d’un amplificateur MOS source commune

www.emse.fr/~dutertre/enseignement.html - 2015 4

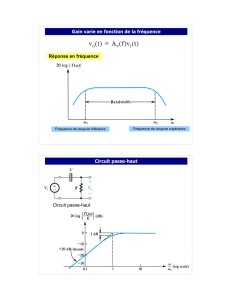

4. Fonctionnement dynamique (AC) de l’amplificateur.

Connecter l’entrée Vin de l’amplificateur à un générateur de signaux délivrant une tension

sinusoïdale d’amplitude ~ 50 mV à la fréquence 1 kHz. Observer Vout à l’oscilloscope.

Compte-rendu :

4.1. Relever la forme du signal de sortie Vout. En déduire le gain petits signaux.

Commentaire ?

4.2. Que se passe-t-il lorsque l’amplitude du signal sinusoïdal augmente un peu ?

moyennement ? fortement ? Vous illustrerez vos réponses.

4.3. Pour RD = 1 kΩ et Vin,amplitude = 50 mV, trouver la fréquence de coupure du montage.

4.4. Visualiser Vin et Vout lorsque f : 1 kHz → fc. Commentaire ?

4.5. Question subsidiaire : Remplacer la résistance de charge RD=1 kΩ par une résistance

de 2,2 kΩ. Reprendre les questions précédentes (4.1 et 4.2). Commentaire ?

Bibliographie.

Sujet de TP adapté de :

Experiment 761 – AC Behavior of Semiconductor Devices, Institute of Nanoelectronics,

Hamburg University of Technology, 2012.

Emploi des condensateurs : document de Serge Dusausay

http://membres.multimania.fr/cepls/condensateur/condensateur.pdf

Annexe.

Polarité du transistor MOS VN2222 : vue 3D (fig. 5 gauche) et vue de dessus (fig. 5 droite).

Fig. 5 – Polarité VN2222.

© Semiconductor Components Industries, LLC, 2004

September, 2004 − Rev. 3

1Publication Order Number:

VN2222LL/D

VN2222LL

Preferred Device

Small Signal MOSFET

150 mAmps, 60 Volts

N−Channel TO−92

Features

•Pb−Free Packages are Available*

MAXIMUM RATINGS

Rating Symbol Value Unit

Drain −Source Voltage VDSS 60 Vdc

Drain−Gate Voltage (RGS = 1.0 M!) VDGR 60 Vdc

Gate−Source Voltage

− Continuous

− Non−repetitive (tp ≤ 50 "s)

VGS

VGSM

±20

±40

Vdc

Vpk

Drain Current

− Continuous

− Pulsed

ID

IDM

150

1000

mAdc

Tot al Pow er Di ssi pat ion @ TA = 25°C

Derate above 25°C

PD400

3.2

mW

mW/°C

Operating and Storage Temperature Range TJ, Tstg −55 to

+150

°C

Maximum ratings are those values beyond which device damage can occur.

Maximum ratings applied to the device are individual stress limit values (not

normal operating conditions) and are not valid simultaneously. If these limits

are exceeded, device functional operation is not implied, damage may occur

and reliability may be affected.

THERMAL CHARACTERISTICS

Characteristic Symbol Max Unit

Thermal Resistance, Junction−to−Ambient R#JA 312.5 °C/W

Maximum Lead Temperature for

Soldering Purposes, 1/16# from case

for 10 seconds

TL300 °C

*For additional information on our Pb−Free strategy and soldering details, please

download the ON Semiconductor Soldering and Mounting Techniques

Reference Manual, SOLDERRM/D.

VN22

22LL

AYWW

D

G

TO−92

CASE 29

STYLE 22

N−Channel

S

123

1

Source

3

Drain

2

Gate

150 mA, 60 V

RDS(on) = 7.5 !

Preferred devices are recommended choices for future use

and best overall value.

See detailed ordering and shipping information in the package

dimensions section on page 2 of this data sheet.

ORDERING INFORMATION

A= Assembly Location

Y= Year

WW = Work Week

MARKING DIAGRAM

& PIN ASSIGNMENT

http://onsemi.com

6

6

7

7

1

/

7

100%