Etude et fabrication de MOSFET de la filière III-V

1

THESE

UNIVERSITE LILLE1 SCIENCES ET TECHNOLOGIES

ECOLE DOCTORALE SCIENCES POUR L’INGENIEUR

Pour obtenir le titre de

Docteur de l’Université Lille1 Sciences et Technologies

Spécialité

Electronique

Par

Jiongjiong MO

Etude et fabrication de MOSFET de la filière III-V

Thèse dirigée par : Prof. Sylvain BOLLAERT

Soutenue le 11/07/2012

Mme Mireille MOUIS Rapporteur

Mr Thierry BARON Rapporteur

Mr Christophe GAQUIERE Examinateur

Mr Guilhem LARRIEU Examinateur

Mr Michel RENVOISE Examinateur

Mr Sylvain BOLLAERT Directeur de thèse

Mr Nicolas WICHMANN Co-encadrant de thèse

N° d’ordre: 40844

Thèse de Jiongjiong Mo, Lille 1, 2012]

© 2012 Tous droits réservés.

http://doc.univ-lille1.fr

2

Thèse de Jiongjiong Mo, Lille 1, 2012]

© 2012 Tous droits réservés.

http://doc.univ-lille1.fr

3

Remerciements

Ce travail de thèse a été réalisé dans le cadre d’un projet ANR MOS III-V au sein d’IEMN

avec la collaboration de différents laboratoires de recherche y compris l’IEF de Paris pour la

simulation Monte Carlo du composant, l’OMMIC de Paris, le CEA-LETI de Grenoble pour la

déposition de l’oxyde, le CIMAP de Caen pour l’image TEM et la groupe Epiphy au sein

d’IEMN pour la préparation du substrat. Je tiens à remercier Monsieur le professeur Alain

Cappy, ancien directeur de l’IEMN, Monsieur Lionel Buchaillot, directeur de recherche

CNRS et actuel directeur de l’IEMN pour m’avoir accueilli au sein de laboratoire d’IEMN

pendant ces durées du travail.

Je remercie Monsieur le professeur Gilles Dambrine, professeur de Lille1, ancien responsable

du groupe Anode et Monsieur le professeur Francois Danneville, professeur de Lille1,

responsable du groupe ANODE actuel, pour m’avoir accueilli au sein du groupe.

Je remercie Madame Mireille Mouis, responsable de recherche à l’INP Grenoble et Monsieur

Thierry Baron, directeur de recherche à CEA Grenoble, pour l’honneur qu’ils m’ont fait en

acceptant d’être rapporteurs de ce travail de thèse.

Je remercie également Monsieur Christophe Gaquiere, professeur à l’Université des Sciences

et Technologies de Lille, Monsieur Guilhem Larrieu, chargé de recherche à LAAS Toulouse

et Monsieur Michel Renvoise,chercheur de OMMIC de participer à ce jury en tant

qu’examinateurs.

Je tiens à remercier mon directeur de thèse, Monsieur Sylvain Bollaert, professeur à Lille1,

pour m’avoir encadré au cours de cette thèse. Grâce aux nombreuses discutions, Sylvain m’a

permis d’avancer mon travail. Je remercie également Monsieur Nicolas Wichmann, maître de

conférences à Lille1, qui a co-encadré ce travail avec l’aide et les conseils m’ont permis de

progresser efficacement.

Je remercie aussi tous les membres du groupe ANODE y compris les permanents Yannick

Roelens et Mohammed Zaknoune pour les discussions. Je remercie aussi Xavier Wallart et

Thèse de Jiongjiong Mo, Lille 1, 2012]

© 2012 Tous droits réservés.

http://doc.univ-lille1.fr

4

Ludovic Desplanque du groupe Epiphy pour m’avoir fourni les échantillons d’épitaxie pour

travailler au dessus.

Je remercie également à mes collègues post-docs, thésards, pour leur soutien et amitié :

Nicolas, Yoann, Cyrille, Phillippe, Nan, Aurélien, Albert, Arame, Laurent, Jinshan, Julien,

David. Aurélien m’a transmis toutes ses connaissances avec ses premiers résultats dans ce

projet MOS III - V.

Je remercie également Sylvie Lepilliet et Vanessa Sbrugnera-Avramovic de centrale de

caractérisation, qui m’ont appris de la mesure. Et aussi Marc Francois, Yves Deblock,

Francois Vaurette, Pascal Tilmant pour la lithographie électronique et optique, Christiane

Legrand pour la gravure sèche, André Leroy, Annie Fattorini pour la métallisation, Christophe

Boyaval pour la caractérisation MEB, et David Troadec pour la préparation de lame TEM de

centrale de technologies.

Thèse de Jiongjiong Mo, Lille 1, 2012]

© 2012 Tous droits réservés.

http://doc.univ-lille1.fr

5

Table des matières

Introduction générale: .............................................................................................................9

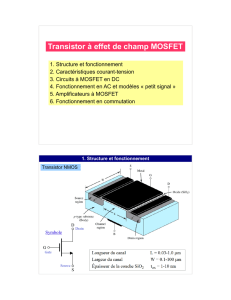

Chapitre 1 Introduction aux Transistors MOSFET de la filière III-V ..................................... 15

1.1 Contexte et enjeux sociétaux ........................................................................................ 15

1.1.1 Fin de la loi de Moore ............................................................................................ 15

1.1.2 L’exigence de l’intelligence ambiante .................................................................... 17

1.2 Principaux paramètres d’un MOSFET.......................................................................... 20

1.2.1 En régime statique ................................................................................................. 20

1.2.1.1 Tension de bande plate VFB .............................................................................. 20

1.2.1.2 Caractéristiques log(Id)=f(VGS)......................................................................... 20

1.2.1.3 Courant de grille .............................................................................................. 23

1.2.1.4 Transconductance ............................................................................................ 23

1.2.1.5 Conductance de sortie ...................................................................................... 23

1.2.1.6 Défaut d’interface ............................................................................................ 23

1.2.1.7 Mobilité effective du canal............................................................................... 25

1.2.1.8 Densité d’états d’un matériau DOS .................................................................. 25

1.2.2 En régime dynamique ............................................................................................ 26

1.3 Consommation de puissance : défi et challenge du ‘Beyond CMOS’ ............................ 27

1.4 Matériaux .................................................................................................................... 30

1.5 Architectures du transistor basse consommation........................................................... 32

1.5.1 MOSFET vs. HEMT .............................................................................................. 32

1.5.2 Architectures alternatives ....................................................................................... 34

1.6 Technologie des MOSFET III-V : défis et contraintes .................................................. 37

1.6.1 L’oxyde sur un matériau III-V : défi majeur de la technologie des MOSFET III-V 37

1.6.1.1 Technique de dépôt d’oxyde ............................................................................ 37

1.6.1.2 Défauts dans l’oxyde Al2O3 (charge fixe)......................................................... 39

1.6.1.3 Défauts à l’interface d’oxyde/semiconducteur .................................................. 40

1.6.1.4 Techniques de passivation : ............................................................................. 40

1.6.2 Matériaux III-V et substrat ..................................................................................... 41

1.6.3 Budget thermique .................................................................................................. 42

1.7 Etat de l’art des MOSFET III-V ................................................................................... 43

1.7.1 Défaut d’interface entre l’oxyde et le semiconducteur ............................................ 43

1.7.2 Comportement sous le seuil ................................................................................... 44

1.7.3 Mobilité effective, courant de drain et transconductance ........................................ 46

1.7.4 Performances fréquentielles ................................................................................... 48

1.8 Les objectifs du travail ................................................................................................. 50

Bibliographie: ....................................................................................................................... 53

Chapitre 2 Fabrication et caractérisation de MOSFET In0.53Ga0.47As .................................... 63

2.1 Introduction ................................................................................................................. 63

2.2 Fabrication et caractérisation de MOSFET In0.53Ga0.47As en technologie « Gate-First » :

structure de référence............................................................................................................ 63

2.2.1 Procédé de fabrication et structure épitaxiale des MOSFET In0.53Ga0.47As en

technologie « Gate-First » ................................................................................................. 63

2.2.1.1 Couche épitaxiale : .......................................................................................... 64

2.2.1.2 Définition de la grille ....................................................................................... 65

2.2.1.3 Masque MOSFET InGaAs multi-doigts de grille ............................................. 67

2.2.2 Briques technologiques de fabrication .................................................................... 69

Thèse de Jiongjiong Mo, Lille 1, 2012]

© 2012 Tous droits réservés.

http://doc.univ-lille1.fr

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

81

81

82

82

83

83

84

84

85

85

86

86

87

87

88

88

89

89

90

90

91

91

92

92

93

93

94

94

95

95

96

96

97

97

98

98

99

99

100

100

101

101

102

102

103

103

104

104

105

105

106

106

107

107

108

108

109

109

110

110

111

111

112

112

113

113

114

114

115

115

116

116

117

117

118

118

119

119

120

120

121

121

122

122

123

123

124

124

125

125

126

126

127

127

128

128

129

129

130

130

131

131

132

132

133

133

134

134

135

135

136

136

137

137

138

138

139

139

140

140

141

141

142

142

143

143

144

144

145

145

146

146

147

147

148

148

149

149

150

150

151

151

152

152

153

153

154

154

155

155

156

156

157

157

158

158

159

159

160

160

161

161

162

162

163

163

164

164

165

165

166

166

167

167

168

168

169

169

170

170

171

171

172

172

173

173

174

174

175

175

176

176

1

/

176

100%