Aide-mémoire VHDL

Aide-mémoire VHDL

Description Exemple

entity entity nom_entite is

port(

CLK, RESET : in std_logic;

SW : in std_logic_vector(7 downto 0);

LED : out std_logic_vector(7 downto 0);

end nom_entite;

Les types à utiliser: std_logic et std_logic_vector

Description Exemple

entity avec paramètres

entity nom_entite is

generic (

TAILLE : integer := 8);

port(

CLK, RESET : in std_logic;

SW : in std_logic_vector(7 downto 0);

LED : out std_logic_vector(7 downto 0);

end nom_entite;

Les types à utiliser: std_logic et std_logic_vector

Description Exemple

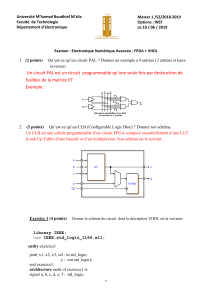

architecture architecture nom_arch of nom_entite is

-- declaration components

-- declaration signaux

Signal cmp : integer range 0 to 63;

Begin

-- Suite d'instructions concurrentes;

-- comme affectation, with-select, when-else,

-- process

end nom_arch;

Description Exemple

Déclaration de

component Component UART

Port (

CLK : in STD_LOGIC;

DATA : in STD_LOGIC_VECTOR (7 downto 0);

STRB : in STD_LOGIC;

EN_19200 : in std_logic;

TX : out STD_LOGIC;

BUSY : out std_logic);

end component ;

Partie "port" doit être identique à l'entité

correspondant

Description Exemple

Instanciation de

component Un_label: UART

Port map(

CLK => MCLK,

DATA => b_donnee,

STRB => strb,

EN_19200 => enable,

TX => TX,

BUSY => occupe);

Description Exemple

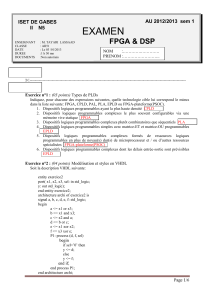

when –else

SORTIE <= "11" when sel='1' else "00";

Ou encore

SORTIE <= "11" when strb = '1' else

"10" when BTN = '1' else

"00";

Une commande

concurrente Un circuit combinatoire pour réaliser les tables de

vérité.

Description Exemple

With – select

with control select

SORTIE <=

"11" when 0,

"10" when 1,

"01" when 2,

"00" when others;

Une commande

concurrente Un circuit combinatoire pour réaliser les tables de

vérité.

Description Exemple

If elsif else

if count = 0 then

AN <= "0111";

elsif count = 1 then

AN <= "1011";

elsif count = 2 then

AN <= "1101";

else

AN <= "1110";

end if;

Une commande

séquentielle A utiliser dans les process ou des fonctions

Description Exemple

case Case count is

when 0 =>

AN <= "0111";

when 1 =>

AN <= "1011";

When 2 =>

AN <= "1101";

when others =>

AN <= "11110";

end case;

Une commande

séquentielle A utiliser dans les process ou des fonctions

Description Exemple

Création d'un signal

"trig" à partir d'une

horloge

cmp : integer range 0 to 5207;

GENE_19200:process(CLK)

begin

if CLK'event and CLK='1' then

en_19200 <= '0';

cmp <= cmp + 1;

if cmp = 5207 then

en_19200 <= '1';

cmp <= 0;

end if;

end if;

end process;

En_19200 est à la fréquence 19200 Hz si CLK est à

100 MHz.

Chaque impulsion de en_19200 ne dure qu'une seule

cycle d'horloge

Note important: La taille du "cmp" est de:

log2(5207)=12.34 13 bits, il peut aller donc

jusqu'à 2

13

-1=8191. Ce signal peut donc dépasser

5207.

Description Exemple

Déclaration de type Type T_ETAT is (repos, envoi, tempo, fin);

Signal etat, etat_future : T_ETAT := repos;

Remarquer comment les signaux sont initialisés. Ceci

est utile pour la simulation.

Description Exemple

Création de mémoire Une mémoire de 16 cases chacune sur 8 bits:

Type t_memo is array (0 to 15) of

std_logic_vector(7 downto 0);

signal memo : t_memo;

constant memo_rom : t_memo :=("11001100",

"00001111", … , "11111111");

Description Exemple

Un process synchrone

avec CLK Proces(CLK) –- pas d'autre signal dans

--la liste de sensibilité

begin

if CLK'event and CLK = '1' then

-- une suite d'instructions séquentielles

end if;

end process;

ATTENTION - Aucune autre instruction entre "begin" et "if";

- Aucune autre instruction entre "end if" et "end

process".

Description Exemple

Détection d'un front

sur un signal "non

CLK". Ici on effectue

une action sur le

front montant de BTN.

Proces(CLK)

begin

if CLK'event and CLK = '1' then

ex_btn <= BTN;

if ex_btn = 0 and BTN = '1' then

-- une suite d'instructions séquentielles

end if;

end if;

end process;

Attention: Ne pas utiliser

if BTN'event and BTN = '1' then

car on a supposé que BTN n'est pas un signal horloge

1

/

3

100%