Projets Automne 2015 - Polytechnique Montréal

Projets

GBM8320 – Dispositifs médicaux intelligents

(DMI 2015)

Mohamad Sawan, professeur

Mohamed Zgaren, chargé de laboratoire

Département de génie électrique

Polytechnique Montréal

Présentation des projets

Local M2204

Pavillon Lassonde

Décembre 2015

GBM8320, Projets (suite)

Session Automne 2015

Page 2 de 43

GBM8320-Dispositifs Médicaux intélligents (DMI’15)

Présentation de projets

Mardi 10 décembre 2015, 12h45-18h00

P#

Heure

Auteur

Titre du projet

Page

Programme

2

Formulaire d’évaluation

3

13h40 Début

1

12h45

Belzil, A.

Conception d’un micro stimulateur pour tissu

cardiaque à étages de sorties multiples

4

2

13h10

Boubée de Gramont, F.

Biocapteur CMOS pour la détection et la mesure

de la concentration de neurotransmetteurs

8

3

13h35

Campbell, P.

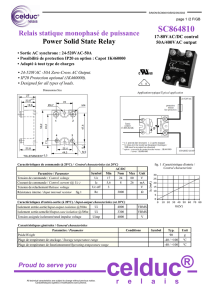

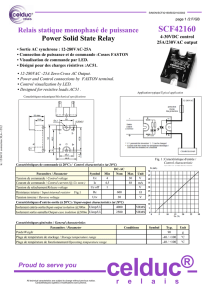

Convertisseur AC/DC de faible puissance pour

l’interface d’un lien inductif

12

4

14h00

Diouf, Y.

Filtre passe-bande en technologie CMOS pour

l’acquisition de signaux biologiques

16

14h25 Pause

Break

5

14h45

Hashemi N., F.

A Low Voltage CMOS Bandgap Voltage

Reference for Biomedical Application

20

6

15h10

Honarparvar, M.

Semi-time Mode Analog Front-end Compatible

with Time Domain Incremental TDC

24

8

16h00

Laurent, É.

Conception d’un ampli d’instrumentation pour

mesurer l’ECG de rongeurs

32

7

15h35

Najarpour F., A.

A 60-dB CMOS Signal Amplifier for Wireless

Extracellular Neural Recording System

28

9

16h25

Trigui, A.

Quadrature Carrier Width Modulation Front-

End Demodulator for Micro-Implants

36

10

16h50

Yabi, N.

Un filtre préliminaire passe-bande 0.4-60Hz

réalisé avec une configuration OTA-C 1.8V,

CMOS 180nm

40

17h15 Fin

Conception d’un micro stimulateur pour tissu cardiaque à étages de sorties

multiples

Par Antoine Belzil

Abstract - Cet article décrit la conception d’un stimulateur

pour un tissu afin de lui permettre de différencier ses

cellules souches pluripotentes en cellules cardiaque

automatique dans le but ultime de trouver une alternative

aux pacemakers électriques. La stimulation active produite

par le système est créée par l’alternance de phase de l’ordre

des nanosecondes afin de n’utiliser un condensateur de

petite taille, mais d’obtenir un courant traversant le tissu en

continu. Deux modèles de tissu ont permis la validation du

circuit, un linéaire et l’autre segmentaire, ce dernier

permettant une analyse électrique à l’intérieur du tissu. Les

résultats obtenus démontrent un potentiel aux bornes du

tissu de 8.35V/cm à 16.58V/cm, quoique ces résultats

puissent être réduits en jouant sur le courant imposé dans le

circuit.

I. Introduction

Les bradyarythmies correspondent aux conditions de

rythmes cardiaques faibles ou inappropriés. Dans la

plupart des cas, ces conditions peuvent être réglées par

l’implantation d’un pacemaker électronique. Ces

derniers ne sont pas toutefois exempts de leur lot de

complications. Il serait alors possible de contourner ces

complications et les limitations des pacemakers

électroniques si un regain du fonctionnement normal

du nœud sinusal ou l’automatisation de façon

biologique était possible. Dans l’objectif de développer

la seconde option à-travers le développement de patchs

biologiquement ingéniés à partir de cellules

pluripotentes, l’optimisation d’un système de stimuli

électrique miniature est requis. Le présent ouvrage

traite la conception d’un tel système permettant la

stimulation d’un tissu cardiaque (myocarde) simulée

grâce à une stimulation en alternance de phase au

travers multiples étages de sorties et un système de

protection du tissu grâce à un condensateur de taille

minimale. Plus précisément, l’objectif était de permette

une stimulation d’au moins 5V/cm, ce qui est

caractéristique du myocarde natif [1], grâce à trois

étages de sorties au travers un tissu simulé par un

réseau de résistance et condensateur représentant un

tissu cardiaque. Le circuit conçu devrait être de taille

assez petite pour son addition à une lamelle de

microscope où le tissu cardiaque réel sera développé.

II. Méthodologie

La première partie consistait à la réalisation d’un tissu

cardiaque formé de condensateurs et résistances, la

seconde, à la conception d’un étage pour générer les

phases de stimulations requises, et la suivante, à la

réalisation d’un étage de sortie permettant la

génération d’un voltage continu aux bornes de sortie

en alternance avec une phase de relaxation. La

complexité de cette dernière provient du fait qu’un

condensateur permettant la protection du tissu pour

une telle stimulation en continu est très élevée et prend

donc beaucoup de place sur un circuit. La dernière

partie consistait en la mise en commun des trois

premières parties, avec une alimentation de 1.8V que

l’optique du projet ne considérait pas et qui a donc été

traité comme idéal et déjà présente sur la lamelle.

Plusieurs étages de sortie seront utilisés comme dans

les travaux de Soulier et al [2].

Dans ce projet, deux représentations du myocarde ont

été réalisées. La première est sa représentation par une

résistance de 100K ohms. Cette valeur provient du

choix d’un tissu représenté simplement comme la

combinaison de 10 cellules d’impédance interne infinie

distancées également de 100µm avec une résistance

entre elle de 100 ohms-cm [3]. Le tissu fut simplement

représenté ainsi pour ne se concentrer que sur le circuit

de stimulation et pour simplifier la propagation des

potentiels d’action le long des fibres musculaires.

La seconde est une couche 2D divisée en segments de

100µm x 100µm. Dans cette couche, les sarcolemmes

et l’espace intracellulaire sont représentés de manière

similaire aux travaux de Spach et Heidlage [4].

Figure 1 : Schéma du modèle segmentaire du myocarde

Chaque circuit résistance (Rm) et condensateur (Cm)

représente les faces supérieures et inférieures du

segment de la couche de tissu. Le tissu sera considéré

isotrope afin d’éviter les complications reliées aux

chemins préférentiels de propagation. La

représentation 2D sera donc homogène avec des

résistances de couplages (Ri et Ri’) égales (figure 1).

Cette représentation permet un réalisme plus élevé et la

possibilité de faire des analyses plus détaillées sur la

propagation du courant à l’intérieur du tissu. Le

tableau 1 liste les valeurs des composantes utilisées

pour la réalisation des modèles 2D. Les valeurs sont

basées sur les travaux de Joyner et Spach [3] [4].

Table 1 : Composants électriques du tissu cardiaque

Composantes

Modèle linéaire

Modèle

segmentaire

Rm

∞

1000 Ω·cm2

Cm

0

1µF/ cm2

Ri

100 Ω·cm

100 Ω·cm

Le générateur de phase fut conçu de façon à permettre

des phases 1 et 2 alternant à la fréquence donnée par

l’entrée 1 pour une durée déterminée par l’entrée 2.

Ces phases produisent une sortie à voltage de 0

lorsqu’actives permettant dans l’étage de sortie

l’ouverture et la fermeture des switchs. De plus, durant

la phase active de l’entrée 2 où les phases 1 et 2 sont

actives, la phase 3 est générée en continu à un voltage

égal à Vdd. Le générateur a été conçu pour prendre en

entrée des ondes carrées. Comme la fréquence

d’alternance de la phase 1 et 2 est très élevée, les

portes logiques composant le circuit furent réalisées à

partir de transistors seulement afin de réduire le temps

d’élévation et de chute du courant et de rendre la sortie

la plus carrée possible. Également, des expériences sur

Cadence ont démontré que l’utilisation en série de

deux inverseurs permet une génération d’onde encore

plus carrée. La figure 2 présente la schématique

réalisée pour le générateur de phase ainsi que ses

portes logiques.

Figure 2 : a) Porte logique NAND, b) porte logique NOT et c)

circuit du générateur de phase utilisant portes logiques a) et b)

L’étage de sortie fut réalisé à l’aide de transistors nmos

et pmos, et d’un condensateur. Dans un système de

stimulation, un condensateur peut être mis en série

avec les électrodes afin de rendre la stimulation

sécuritaire. Dans la période de stimulation, le

condensateur accumule des charges. Dans la phase de

repos ou décharge, le courant anodique neutralise les

charges accumulées. Dans le cas d’un bris des semi-

conducteurs, grâce à au condensateur il n’y aura pas

d’exposition prolongée du tissu au courant DC une fois

saturée. Cependant, comme une stimulation est d’une

durée de l’ordre des millisecondes, les capacités

requises sont de plusieurs µF [5]. Le volume des

condensateurs étant dans les alentours de 5mm3/µF [5]

pour un système comportant plusieurs étages de sorties

les condensateurs prendrait autant sinon plus d’espace

que le reste des composantes du système. Selon

l’équation 1 décrivant la relation capacité-courant, il

est possible de voir l’impact du temps de stimulation

sur la capacité pour une différence de potentiel donnée.

La capacité utilisée pour les simulations fut de 50nF,

soit plus de 100 fois plus petite que celles

normalement utilisées pour des circuits de stimulation.

𝐼𝑠= 𝐶 𝑑𝑉

𝑑𝑡 (1)

Le principe du circuit de sortie repose sur l’alternance

rapide (MHz ou GHz) entre les phases 1 et 2 durant la

stimulation afin de permettre l’utilisation de capacités

très faibles. Comme ces deux phases permettent

chacune la stimulation avec la même amplitude durant

la même période de temps en alternance, si le courant

passe au travers de la résistance ou tissu dans le même

sens, le résultat final est équivalent à une stimulation

en continu. Afin de permettre ce trajet au courant et un

courant au sens alternant dans le condensateur, un pont

de diode a été utilisé. Ces diodes furent dans un

premier temps idéales et par la suite réalisées à l’aide

d’un seul transistor monté en diode, soit pour un nmos,

la Gate connectée à la Source. Pour trouver les

paramètres de chacune des diodes, une analyse

paramétrique fut réalisée grâce au logiciel Cadence.

Comme pour l’étage de génération de phase, les

switchs ont été réalisés avec des transistors seulement

afin de permettre une transition quasi-parfaite entre

chacune. Les transistors de la technologie 0.18 que

nous utilisons pour le présent ouvrage fonctionnent

très bien aux fréquences désirées. Ces switchs agissent

comme des portes logiques « NOT » en plus d’ouvrir

et fermer. C’est pourquoi le générateur de phase

produit une tension nulle pour permettre aux switchs

d’ouvrir. Les valeurs des transistors contrairement à

celles des transistors des portes logiques du générateur

ont été optimisées afin de permettre une plus grande

tension aux bornes de sortie. Dans le cas des switchs,

les transistors pmos utilisés auraient pu être remplacés

par des résistances. Leurs valeurs permettent une

grande impédance, soient W=500nm et L=10µm. Les

transistors nmos permettent le changement entre les

deux différences de potentiel, et pour les optimiser,

leur impédance fut minimisée. Leur dimension sont

ainsi W=8µm et L=180nm. Ces valeurs optimales ont

été trouvées à l’aide d’analyses paramétriques sur le

logiciel Cadence.

Figure 3 : Schéma de l’étage de sortie

Le circuit final de l’étage de sortie est présenté à la

figure 3. La source de courant Istim est idéale dans le

circuit. L’objectif du projet ne nécessitant pas une

faible consommation de courant, la source fut, pour les

simulations finales, fixée à 800µA. Le courant peut

être ajusté lorsqu’une résistance beaucoup plus faible

que 100k ohms est utilisée, soit lorsqu’un tissu plus

petit est utilisé. Pour obtenir le même courant de

stimulation avec une plus faible source de courant, il

serait possible d’utiliser un miroir de courant à l’entrée

du système.

Le circuit complet permettant dans un premier temps la

stimulation de la résistance de 100k ohms et dans un

second celui du tissu (figure 4) fut réalisé en

combinant le générateur de phase, trois étages de sortie

et la résistance ou tissu. La différence de potentiel fut

relevée aux bornes de la résistance et aux bornes

centrales du tissu. Pour le tissu, deux analyses furent

réalisées, soient une stimulation à un étage de sortie au

centre du tissu et une autre avec les trois étages répartis

également aux extrémités du tissu.

Figure 4: Circuit final du projet

III. Résultats

Le générateur de phase permet la production des trois

phases désirées, soient l’alternance des phases un et

deux de 1.8V à 0V durant la stimulation et la mise à

0V de la phase trois durant la relaxation ou stimulation

passive. Cependant, malgré l’utilisation de transistor

permettant une variation de phase rapide, un décalage

de 4 ns peut être observable entre les phases un et

deux. Les entrées du générateur alternèrent de 1.8V à

0V, l’entrée un (haut) pour 500ns sur 1µs et la seconde

(bas) pour 10µs sur 20µs. À des fins de présentation

des résultats, la stimulation sur Cadence ne fut que de

10µs, mais en réalité elle pourrait être plus grande sans

que les résultats varient pour autant.

La figure 5 montre la différence de potentiel aux

bornes de la résistance de 100k ohms. La différence de

potentiel aux bornes atteint 16.58V pour la stimulation

active et 0 lors de la période de repos. Le décalage des

phases produit pour un bref instant une baisse dans le

courant passant au travers la résistance ou tissu. Ceci

produit alors des pics ressemblant à des fonctions de

Dirac à tous les changements de phases. Leur

amplitude ne représentant que le tiers de l’amplitude

totale pour une durée moindre de 5 ns, leur effet est

négligeable sur la durée de stimulation. De cette

différence de potentiel, un courant de stimulation égale

à 166µA dans la résistance est trouvable.

Figure 5 : Différence de potentiel aux bornes de la résistance de

100k ohm durant la stimulation

La figure 6 présente la différence de potentiel aux

bornes du tissu lors de la stimulation au centre

seulement (6a) et lors d’une stimulation à trois sorties

également réparties (6b). La différence de potentiel

dans les deux cas varie de façon similaire à la

résistance de 100k ohms, avec des amplitudes de

8.35V pour un étage de sortie et 14.27V et 14.55V

pour trois étages de sortie, où l’amplitude la plus

élevée est relevée aux extrémités du tissu.

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

1

/

42

100%

![III - 1 - Structure de [2-NH2-5-Cl-C5H3NH]H2PO4](http://s1.studylibfr.com/store/data/001350928_1-6336ead36171de9b56ffcacd7d3acd1d-300x300.png)