Évolution des technologies des composants

CCT Rex COTS Myriade 8 janvier 2008 1

Évolution des technologies des

composants commerciaux

Philippe Perdu DCT/AQ/LE

CCT Rex COTS Myriade 8 janvier 2008 2

Objectifs de la présentation

¾Composants commerciaux pour applications

professionnelles: Etat des lieux

¾Domaines concernés limités

oNanotechnologie, (V) DSM (90, 65, 45 nm)

oVLSI numériques

• haute performance

• Basse consommation

oNe représente qu’une (petite) partie des composants commerciaux

¾Situer le contexte des VLSI pour applications industrielles,

médicales, militaires et spatiales …

oIndiquer les tendances technologiques pour les années à venir

(horizon 2010 et au delà)

oPrésenter les aspects économiques liés à ces tendances

technologiques et aux marchés

oIdentifier les conséquences principales et les défis importants pour

les petits volumes et fortes contraintes

CCT Rex COTS Myriade 8 janvier 2008 3

Contexte de la nanoélectronique

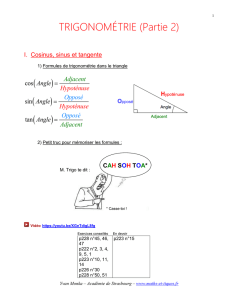

¾Petit rappel de la loi de Moore

oLe facteur d’homothétie S appliquée à la réduction des dimensions

spatiales d’une nouvelle technologie par rapport à la précédente est

constant et égal à 0.7.

oLe nombre de transistors par unité de surface (la densité

d’intégration) double donc à chaque génération.

oC’est une règle empirique qui sert néanmoins d’indicateur à

l’industrie du semiconducteur

oLe changement de technologie se fait tous les 2 ans environ (3 ans au

départ)

¾Des questions fondamentales se posent

oJusqu’à quel moment cette loi sera-t-elle applicable?

• évolutions technologiques

• Éléments économiques

oQuels sont les produits / applications concernés

CCT Rex COTS Myriade 8 janvier 2008 4

Loi de Moore (1)

CCT Rex COTS Myriade 8 janvier 2008 5

Loi de Moore (2)

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

1

/

50

100%

![Logo Myriade - Centre de réadaptation [ La Myriade ]](http://s1.studylibfr.com/store/data/000239065_1-aece08eeda3a23cd4cbfba00319bf79e-300x300.png)