architecture des microprocesseurs derrière votre

1ES102

ARCHITECTURE DES

MICROPROCESSEURS

ES102 / CM8

Couches logicielles

Architecture

Micro-architecture

Logique/Arithmétique

Circuit logique

Circuit analogique

Dispositif

Physique

1 2

3 4

5

67

8

9

9

7

01/12/1990

(INTRODUCTION)

2ES102/CM8

DERRIÈRE VOTRE PROGRAMME C …

00000000101000010000000000011000

00000000100011100001100000100001

10001100011000100000000000000000

10001100111100100000000000000100

10101100111100100000000000000000

10101100011000100000000000000100

00000011111000000000000000001000

swap(int v[],int k)

{ int temp;

temp=v[k];

v[k]=v[k+1];

v[k+1]=temp;

}

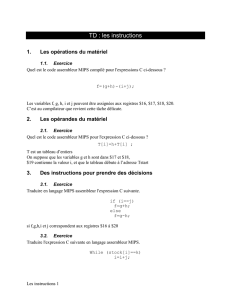

swap: sll $2 $5 2

add $2 $4 $2

lw $15 0($2)

lw $16 4($2)

sw $16 0($2)

sw $15 4($2)

jr $31

compilation

langage de l’embarqué,

du calcul intensif et des

systèmes d’exploitation

langage assembleur

(variante lisible du

langage machine)

C

langage machine

! IN102

exécution Pour ce cours, choix

de la famille de micro-

processeurs MIPS

instruction élémentaire

exécutée en une (à quelques)

période(s) d’horloge

processus

dépend

du type de

machine

visée

programme s’exécutant

sur une machine

3ES102/CM8

BESOIN DE MÉMOIRE …

0110 ···············1010

0001 ···············1011

1111 ···············1111

1010 ···············1100

·

·

1100 ···············0110

0100 ···············1111

contenu mémoire

adresse

binaire / numérique

0 ···0000 0

0 ···0001 1

0 ···0010 2

0 ···0011 3

· ·

· ·

1 ···1110 2n-2

1 ···1111 2n-1

largeur : l bits

profondeur :

2n mots

capacité : l · 2n bits

n bits

bit porté par une

cellule mémoire,

détaillée au CM9

(en transistors)

l

nM

adresse

dout

din

l

RW

• mémoire = tableau de bits, de largeur l, dont chaque ligne :

–possède une adresse propre : son numéro, sur n bits

–est accessible en lecture (RW = 1) ou en écriture (RW = 0)

• sur présentation de son adresse

séquencement

spécifique

R : read

W : write

4ES102/CM8

… POUR MÉMORISER …

•des données

typiquement sur 32 bits ou un multiple

•sauf les caractères, sur 8 bits (= 1 octet)

–type char du C

" adressage octet par octet " l=8

" donnée 32 bits sur 4 lignes successives

•des adresses

sur 32 ou 64 bits

typiquement

" espaces adressables :

232 = 4 gigaoctets (étroit)

264 = 16 exaoctets (immense)

•des instructions

= signaux de commande

de CD, et plus…

•en partie codés

········

11111111

11111111

11111111

11111111

01000101

01010011

00110001

00110000

00110010

00000000

········

int –1 ou

unsigned int

4!294!967!295

char ‘E’

char ‘S’

char ‘1’

char ‘0’

char ‘2’

8

Mémoire

de données

donnée écrite

donnée

adresse lue

32

32 32

RW

MIPS I :

tout en 32 bits

integer

MI MD

une adresse

stockée en mémoire,

ou dans un registre,

est un pointeur

en langage C

et il est

traité comme

une donnée

adresse

Mémoire

d’instructions

instruction lue

32

32

5ES102/CM8

BESOIN DE PLUS DE REGISTRES, AUSSI

Registre

load=1 : chargement nouvelle donnée

load=0 : maintien ancienne donnée

• Multiples variables de calcul au cœur des algorithmes

" Besoin de réaliser des opérations entre de multiples registres

–extrême pauvreté de la «!calculette primitive!» : seulement 2 registres

–à chaque cycle d’horloge, on souhaite pouvoir récupérer le contenu de

n’importe quel couple de registres parmi de multiples accessibles, faire

une opération sur les 2 opérandes ainsi récupérés, et ranger le résultat

dans n’importe quel registre

• C’est un banc de registres qui va répondre à ces besoins

load 1 0

d q

dff

CK

1 0

d q

dff

CK

1 0

d q

dff

CK

1 0

d q

dff

CK

load

CK R

6ES102/CM8

load0

load1

load2

load3

load4

load5

load6

load7

R0

R1

R2

R3

R4

R5

R6

R7

32

Exemple avec 8

registres 32 bits

SW = Select Write 0

1

2

3

4

5

6

7

SW

3

un seul

load à 1

CK

SW

SR1

SR2

data in

data out1

data out2

" 10kt

BANC DE

REGISTRES

sw2’

sw2

sw1’

sw1

sw0’

sw0

Décodeur d’adresse (PC4)

numéro de registre " adresse

décodeur

d_in

SR1

3

32

0

1

2

3

4

5

6

7

SR1 = Select Read 1

d_out1

0

1

2

3

4

5

6

7

SR2

3

32

SR2 = Select Read 2

multiplexeurs numériques 8 vers 1

d_out 2

7ES102/CM8 d_in

load1

load2

load3

load4

load5

load6

load7

R1

R2

R3

R4

R5

R6

R7

32

0

1

2

3

4

5

6

7

SW

3

SR1

3

d_out1

32

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

SR2

3

d_out 2

32

BANC DE

REGISTRES

(2)

multiplexeurs numériques 8 vers 1

décodeur

Registres

n° reg. donnée

lu2 lue2

lu1 lue1

écrit écrite

SR2

SR1

SW

d_out 1

d_out 2

d_in

0

R0 souvent remplacé par la constante

numérique 0 et appelé registre zéro :

- utile pour particulariser certaines opérations

- permet de n’écrire sur aucun registre avec SW=000

inutilisé

Registres souvent nommés

autrement que par leur numéro, selon

certaines spécificités : t0, s1, ra, a2, v0, sp…

8ES102/CM8

ALU

ALU = Unité

Logique &

Arithmétique

Registres

n° reg. donnée

lu2 lue2

lu1 lue1

écrit écrite

SO

+/–

#

=0

>0

÷

a1 b12a0 b0

SOLU

0

r1r0

0

1

2

3

0

1

2

3

=0

LU

CHEMIN DE

DONNÉES POUR

PROCESSEUR

SO :

Select

Operation

Instruction = { SR1, SR2, SO, SW } : les signaux de commande du CD

SR2

SR1

SW

9ES102/CM8

Mémoire

de données

donnée écrite

donnée

adresse lue

ALU

0

1

Registres

n° reg. donnée

lu2 lue2

lu1 lue1

écrit écrite

=0

>0

SO

CHEMIN DE DONNÉES ÉTENDU

1

0

Pas d’échange de données

direct entre mémoire et ALU :

architecture dite load-store

Adresses mémoire élaborées

par l’ALU : ce sont les

pointeurs du langage C R/W

Bus multiplexés

din

Entrée din pour usage ultérieur spécifique

L’instruction { SR1, SR2, SO, SW } se complexifie :

R/W et commandes des MUX en plus

SR2

SR1

SW

10ES102/CM8

CODAGE DES INSTRUCTIONS

• Redondance entre SO, R/W et les commandes des MUX ; cas inutilisés

!on code chaque instruction pour gagner en concision,

en lui attribuant un numéro propre : le code opératoire

•sur 6 bits en MIPS

• SR1, SR2 et SW restent en clair car indépendants/orthogonaux

•sur 5 bits chacun car 32 registres en MIPS I

– instruction structurée en champs successifs

• instruction codée " décodage «!live!» nécessaire

!à la charge de l’UC (unité de commande)

Mémoire

de données

donnée écrite

donnée

adresse lue

ALU

RI op rs rt rd ···

r = reg.

d = dest.

s = source

t = source/dest.

op = code opératoire

RI = Reg. d’instruction

0

1

32

1

0

0

1

Registres

n° reg. donnée

lu2 lue2

lu1 lue1

écrit écrite

5

32

=0

>0

SW

din

R/W

SO

code opératoire sur 6 bits

32

32

SR2

SR1

Exemple ultérieur…

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

1

/

15

100%