Time - LIRIS

C. Wolf!# 1!

INSA-3IF!

Architecture des

Ordinateurs!

Christian Wolf,!

INSA-Lyon, Dép. IF!

Séance 4!

C. Wolf!# 2!

Au Menu!

CM1!ISA : Introduction. Jeux d’instructions,

assembleur.!

TD!La «"Micromachine"» : réalisation d’un processeur

simple sur papier!

CM2!ISA : Encodage; Histoire!

TP!Réalisation de la micromachine sous Logicworks!

CM3!Chemin de données d’un CPU RISC.!

Parallélisme des instructions!

CM4!CPU super-scalaires, multi-threading!

Retour sur les ISA/architectures!

CM5!Hiérarchie mémoire! (Florent De Dinechin)!

TP!Prise en main du contrôleur MSP 430!

CM6!Les GPU !

TD!Micromachine sur papier : les interruptions!

TP!MSP 430 : pile, timer, interruptions!

C. Wolf!# 3!

Sommaire de la séance!

Processeurs multi-scalaires, multi-

threads!

!

!

ARM : architecture!

!

!

!

X86 : ISA + architecture!

!

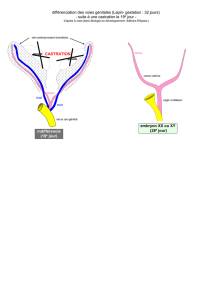

Simultaneous Multithreading

Simultaneous Multithreading

Maximum utilization of function units by independent operations

Time

C. Wolf!# 4!

Après le parallélisme des instructions!

Question : comment obtenir encore plus de performance

pour un seule et unique thread, c.à.d. avec un seul cœur?!

!

Pipeline classique («"processeur scalaire"») :!

Une instruction peut terminer par cycle d’horloge (dans le

meilleur des cas).!

!IF! ID! MEM!EX! WB!

IF! ID! MEM!EX! WB!

IF! ID! MEM!EX! WB!

IF! ID! MEM!EX! WB!

IF! ID! MEM!EX! WB!

C. Wolf!# 5!

Processeur super-scalaire!

IF! ID! MEM!EX! WB!

IF! ID! MEM!EX! WB!

IF! ID! MEM!EX! WB!

IF! ID! MEM!EX! WB!

IF! ID! MEM!EX! WB!

IF! ID! MEM!EX! WB!

IF! ID! MEM!EX! WB!

IF! ID! MEM!EX! WB!

IF! ID! MEM!EX! WB!

IF! ID! MEM!EX! WB!

Plusieurs instructions peuvent terminer par cycle d’horloge

(dans le meilleur des cas).!

Pour x86 : depuis 1993 (Intel Pentium P5)!

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

1

/

43

100%