ARCHITECTURE DES ORDINATEURS

publicité

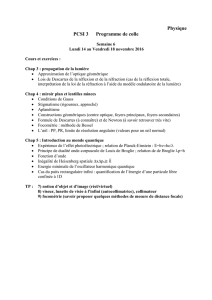

ARCHITECTURE DES ORDINATEURS Filière : InfoTronique Chap. 4 : Architecture et fonctionnement du microprocesseur 8086 Dr. Abdelhakim Khouas Email : [email protected] Département de Physique Faculté des Sciences Objectif de ce chapitre Comprendre l’architecture et le jeux d’instruction du 8086 Architecture interne du 8086 Unité arithmétique et logique (UAL) Unité de commande Traitement et exécution des instructions Programme assembleur Représentation et codage des instruction Jeu d‘instructions du 8086 Architecture – Chap. 4 1 © A. Khouas, 2008 Plan 1. Architecture interne du 8086 Unité d’exécution Unité de transfert ou de commande 2. Fonctionnement du 8086 Programme assembleur Représentation et codage des instructions Traitement et exécution des instructions 3. Jeu d’instruction du 8086 Instructions Instructions Instructions Instructions Instructions Instructions 4. 5. de transfert de données arithmétiques et logiques de décalage et de rotation de comparaison de sauts conditionnels et inconditionnels liées au registre d’état Exemples de codage Conclusion Architecture – Chap. 4 2 © A. Khouas, 2008 Rappel Architecture d’un ordinateur Architecture Von Newmann Réf. : Microprocesseur, support de cours Dr. J. Y. Haggège Architecture – Chap. 4 3 © A. Khouas, 2008 Rappel Les registres du 8086 AX=0FFF BX=0FFF CX=0000 DX=00FF SP=FFEE BP=0000 SI=0000 DI=0000 DS=13B0 ES=13B0 SS=13B0 CS=13B0 IP=0306 NV UP EI PL NZ NA PO NC 4 Registres généraux : AX, BX, CX et DX. Chaque registre général est composé de deux registres de 2 octets (8 bits) (e.g. AX = AH*256 + AL, AH est le registre de poids fort et AL est le registre de poids faible) 2 Registres d’index : SI (Source Index) et DI (Destination Index). 4 Registres de segment : CS (Code Segment), DS (Data Segment), ES (Extra segment), et SS (Stack Segment) 3 registres de pointeur : IP (instruction Pointer), SP (Stack Pointer) et BP (Base Pointer). 1 Registre d’état : F (Flag Register). les flags du registre sont : débordement, retenue, retenue auxiliaire, signe, parité, zéro, interruption, exécution pas à pas. Architecture – Chap. 4 4 © A. Khouas, 2008 1. Architecture interne du 8086 Description du μP 8086 Apparu en 1978 16 bits de données 20 bits d’adresse Boîtier DIP (Dual In-line Package) 40 broches Les adresses et les données sont multiplexés Description du 8086 Réf. : Microprocesseur, support de cours Dr. J. Y. Haggège Architecture – Chap. 4 5 © A. Khouas, 2008 1. Architecture interne du 8086 Démultiplexage des signaux adressses/données Réf. : Microprocesseur, support de cours Dr. J. Y. Haggège Architecture – Chap. 4 6 © A. Khouas, 2008 1. Architecture interne du 8086 Le microprocesseur 8086 est composé principalement de deux unités : 1. Unité d’exécution (Execution Unit EU) 2. Unité d’interfaçage de bus (Bus interface Unit BIU) Architecture – Chap. 4 7 © A. Khouas, 2008 1. Architecture interne du 8086 Architecture interne du 8086 Réf. : Microprocesseur, support de cours Dr. J. Y. Haggège Architecture – Chap. 4 8 © A. Khouas, 2008 1. Architecture interne du 8086 Architecture interne du 8086 Réf. : Principe des microprocesseurs Jaques BAUMANN Architecture – Chap. 4 9 © A. Khouas, 2008 2. Fonctionnement du 8086 Le fonctionnement d’un μP consiste à exécuter un programme en assembleur 8086 Architecture – Chap. 4 10 © A. Khouas, 2008 2.1 Programme assembleur Un programme assembleur est une suite d’instructions précises données par le fabricant du μP et qui sont comprises par le μP Exemple : Programme assembleur du 8086 mov ax,ff mov bx,[35] add ax,bx Architecture – Chap. 4 11 © A. Khouas, 2008 2.2 Représentation et codage des instructions L’instruction est une opération de base qui peut être décodée et exécutée par le μP Format d’une instruction Chaque instruction a un format donné Le format général d’une instruction est : Mnémonique Opérande 1 [Opérande 2] • Mnémonique: est le nom de l’opération • Opérande 1 : est en général un registre ou ne case mémoire • Opérande 2 : est soit un registre, soit une case mémoire, soit une valeur Architecture – Chap. 4 12 © A. Khouas, 2008 2.2 Représentation et codage des instructions Formats des instructions Le format général d’une instruction est : Mnémonique Opérande 1 [Opérande 2] • Mnémonique: est le nom de l’opération • Opérande 1 : est en général un registre ou une case mémoire • Opérande 2 : est soit un registre, soit une case mémoire, soit une valeur Exemples : MOV AX,[00FF] ADD AX,BX STC JMP 0100 Architecture – Chap. 4 13 © A. Khouas, 2008 2.2 Représentation et codage des instructions Chaque instruction est placée en mémoire sous forme codée Cette représentation est appelé code machine Le codage de l’instruction est effectué en décomposant l’instruction en sous groupes de bits appelés champs, spécifiant les caractéristiques de l’instruction. Les différents champs sont : Code opération : code indiquant l’opération (ADD, MOV, SUB, …etc) Type de donnée : 1 pour octet et 0 pour mot (2 octets) Registre : indique le numéro d’un des registres utilisés Mode d’adressage : indique le mode d’adressage (voir ch. mémoire) Architecture – Chap. 4 14 © A. Khouas, 2008 2.2 Représentation et codage des instructions Code opération d’une instruction (opcode) Chaque instruction est codée en binaire et est décodé par le μP lors de l’exécution de l’instruction Exemple : Ci-dessous différents codes de l’instruction MOV donnés par la commande u de debug 13B0:0100 13B0:0103 13B0:0106 13B0:0108 Architecture – Chap. 4 B8FF00 A1FF00 89D8 8B07 MOV MOV MOV MOV 15 AX,00FF AX,[00FF] AX,BX AX,[BX] © A. Khouas, 2008 2.2 Représentation et codage des instructions Exemples de codes opération du 8086 : Architecture – Chap. 4 16 © A. Khouas, 2008 2.3 Traitement et exécution d’une instruction Les étapes d’exécution d’une instruction sont : 1. 2. 3. 4. 5. 6. Chargement de l’instruction courante (registre IP) Incrémentation du pointeur d’instruction Décodage et analyse de l’instruction Localisation et chargement des données Exécution de l’instruction Retour à l’étape 1 Ce cycle s’appelle : Cycle de chargement-décodage-exécution Ou (fetch-decode-excute) cycle Architecture – Chap. 4 17 © A. Khouas, 2008 3. Jeu d’instructions du 8086 Définition : C’est l’ensemble des instructions qui peuvent être exécutées par le μP Il existe plusieurs groupes d’instructions (voir Annexe A des TP) Les instructions de transfert de données Les instructions arithmétiques et logiques Les instruction de décalage et rotation L’instruction de comparaison Les instructions de saut et de branchement Les instructions relatives au registre d’état Architecture – Chap. 4 18 © A. Khouas, 2008 3.1 Instructions de transfert de données Architecture – Chap. 4 19 © A. Khouas, 2008 3.2 Instructions arithmétiques et logiques Addition : ADD opérande1,opérande2 opérande1 ← opérande1 + opérande2 Exemple : add byte ptr [1200H],05H ajoute la valeur 05H au contenu de la case mémoire d’offset 1200H (adressage immédiat). Soustraction : SUB opérande1,opérande2 opérande1 ← opérande1 − opérande2 Architecture – Chap. 4 20 © A. Khouas, 2008 3.2 Instructions arithmétiques et logiques Multiplication : MUL opérande Cette instruction effectue la multiplication du contenu de AL par un opérande sur 1 octet ou du contenu de AX par un opérande sur 2 octets. Le résultat est placé dans AX si les données à multiplier sont sur 1 octet (résultat sur 16 bits), dans (DX,AX) si elles sont sur 2 octets (résultat sur 32 bits). Si opérande sur 1 octet : AX <-- AL * opérande Si opérande sur 2 octets : (DX,AX) <-- AX * opérande Exemple 1: mov al,51 mov bl,32 mul bl → AX = 51 × 32 Architecture – Chap. 4 21 © A. Khouas, 2008 3.2 Instructions arithmétiques et logiques Exemple 2 : mov ax,4253 mov bx,1689 mul bx → (DX, AX) = 4253 × 1689 Exemple 3 : mov al,43 mov byte ptr [1200H],28 mul byte ptr [1200H] → AX = 43 × 28 Exemple 4 : Architecture – Chap. 4 mov ax,1234 mov word ptr [1200H],5678 mul word ptr [1200H] → (DX, AX) = 1234 × 5678 22 © A. Khouas, 2008 3.2 Instructions arithmétiques et logiques Division : DIV opérande Cette instruction effectue la division du contenu de AX par un opérande sur 1 octet ou le contenu de (DX,AX) par un opérande sur 2 octets. Si opérande sur 1 octet : AL=quotient et AH=reste Si opérande sur 2 octets : AX=quotient et DX=reste. Exemples : mov ax,35 mov bl,10 div bl → AL = 3 (quotient) et AH = 5 (reste) mov dx,0 mov ax,1234 mov bx,10 div bx → AX = 123 (quotient) et DX = 4 (reste) Architecture – Chap. 4 23 © A. Khouas, 2008 3.2 Instructions arithmétiques et logiques Instructions logiques OU logique : OR op1,op2 ; ET logique : AND op1,op2 ; OU exclusif : XOR op1,op2 ; Négation : NOT op ; Complément à 1 : NEG op ; op ← not(op) +1. Autre instructions : Architecture – Chap. 4 ADC : addition avec retenue ; SBB : soustraction avec retenue ; INC : incrémentation d’une unité ; DEC : décrémentation d’une unité ; IMUL : multiplication signée ; IDIV : division signée. 24 © A. Khouas, 2008 3.3 Instructions de décalage et de rotation shl dest, op décalage logique gauche dest.0 shr dest, op décalage logique droite 0.dest sar dest, op décalage arithmétique droite S.dest rol dest, op rotation gauche dest ror dest, op rotation droite dest rcl dest, op rot. gauche dest.C rcr dest, op rot. droite C.dest dest == registre ou adresse mémoire OP == 1 ou CL Architecture – Chap. 4 25 © A. Khouas, 2008 3.3 Instructions de décalage et de rotation Architecture – Chap. 4 26 © A. Khouas, 2008 3.3 Instructions de décalage et de rotation Architecture – Chap. 4 27 © A. Khouas, 2008 3.3 Instructions de décalage et de rotation Architecture – Chap. 4 28 © A. Khouas, 2008 3.3 Instructions de décalage et de rotation Architecture – Chap. 4 29 © A. Khouas, 2008 3.4 Instruction de comparaison Instruction de comparaison : CMP opérande1 opérande2 ; --> opérande 1 – opérande2 Cette instruction permet de comparer les deux opérandes et d’activer les flags du registre d’état pour les sauts conditionnels Exemple : mov cmp --> bit al, 23 al, 34 29 – 34 (positionne le bit de carry C et le de signe S, le bit de zéro Z vaut 0) Architecture – Chap. 4 30 © A. Khouas, 2008 3.5 Instructions de sauts et de branchement Instructions de sauts inconditionnels : JMP addr CALL addr RET saut inconditionnel appel sous-programme retour sous-programme Exemple (boucle infinie) boucle : inc ax dec bx jmp boucle Remarques : Avec debug, il faut écrire le code en deux phases, la première permet de récupérer l’adresse de saut. Certains assembleurs utilisent des labels Architecture – Chap. 4 31 © A. Khouas, 2008 3.5 Instructions de sauts et de branchement Instructions de sauts conditionnels / carry: JC addr JNC addr saut si carry=1 saut si carry=0 Instructions de sauts conditionnels / entiers : JE addr JNE addr JZ addr JNZ addr Architecture – Chap. 4 saut saut saut saut si si si si 32 = =/ =0 =/ 0 © A. Khouas, 2008 3.5 Instructions de sauts et de branchement Instructions de sauts conditionnels / entiers non signés: JB addr JA addr JBE addr JAE addr saut saut saut saut si si si si < > <= >= Instructions de sauts conditionnels / entiers signés : JL addr JG addr JLE addr JGE addr Architecture – Chap. 4 saut saut saut saut si si si si < > <= >= 33 © A. Khouas, 2008 3.5 Instructions de sauts et de branchement Autres instructions de sauts conditionnels : JCXZ addr JO addr JNO addr JP addr JNP addr JS addr JNS addr saut saut saut saut saut saut saut si si si si si si si CX vaut 0 débordement (O =1) pas de débordement (O =0) parité (P =1) pas de parité (P =0) signe (S =1) pas de signe (S =0) Les boucles : LOOP addr LOOPE addr LOOPNE addr Architecture – Chap. 4 saut court si le compteur CX est différent de 0 saut court si compteur CX différent de 0 et Z =1 saut court si compteur CX différent de 0 et Z =0 34 © A. Khouas, 2008 3.5 Instructions de sauts et de branchement Exemple : Addition des 5 valeurs se trouvant à l’adresse 1101-1105 13C9:0100 13C9:0103 13C9:0106 13C9:0108 13C9:010C 13C9:010E Architecture – Chap. 4 BA0000 B90500 89CB 02970011 E2F8 CD20 MOV MOV MOV ADD LOOP INT 35 DX,0000 CX,0005 BX,CX DL,[BX+1100] 0106 20 © A. Khouas, 2008 3.5 Instructions de sauts et de branchement Exemple : Addition des valeurs contenu dans la mémoire à partir de l’adresse 400h jusqu’au débordement 13C9:0300 13C9:0303 13C9:0306 13C9:0309 13C9:030B 13C9:030E 13C9:030G Architecture – Chap. 4 BE0004 BB0000 BA0000 0310 0310 71FC CD20 MOV MOV MOV ADD ADD JNO INT 36 SI,0400 BX,0000 DX,0000 DX,[BX+SI] SI,2 0309 20 © A. Khouas, 2008 3.6 Instructions relatives au registre d’état LAHF : copie dans le registre AH la valeur du registre d’état SAHF : copie dans le registre d’état le contenu du registre AH PUSHF : Sauvegarde du registre d’état dans la pile POPF : Récupération du registre d’état de la pile CLC : mise à 0 de l’indicateur de retenue C STC : mise à 1 de l’indicateur de retenue C CMC : complémente l’indicateur de retenue C CLD : mise à zéro de l’indicateur de direction D STD : mise à 1 de l’indicateur de direction D Architecture – Chap. 4 37 © A. Khouas, 2008 4. Exemples de codage Traduction en assembleur de la boucle pour : POUR indice := 1 à n FAIRE action FAIT Transformation : POUR indice := n à 1, pas := -1 FAIRE action FAIT Cette boucle se traduit en assembleur de la manière suivante : POURn: Architecture – Chap. 4 mov cx, n ... action loop POURn 38 © A. Khouas, 2008 4. Exemples de codage Traduction de la boucle Si-Alors-Sinon : SI (condition vraie) ALORS action-alors SINON action-sinon FIN_SI Cette boucle se traduit en assembleur de la manière suivante : calcul de la condition Jcc SINONn action-alors ... JMP FSIn SINONn: action-sinon ... FSIn: ... Architecture – Chap. 4 39 © A. Khouas, 2008 4. Exemples de codage Traduction de la boucle répéter REPETER action JUSQUA (condition vraie) Cette boucle se traduit en assembleur de la manière suivante : REPETER action ... calcul de la condition (positionnement des flags) Jcc REPETER Architecture – Chap. 4 40 © A. Khouas, 2008 4. Exemples de codage Traduction en assembleur de la boucle tant que : TANT-QUE (condition) FAIRE action FIN_TQ Cette boucle se traduit en assembleur de la manière suivante : TQ : calcul de la condition Jcc FTQ action ... JMP TQ FTQ: Architecture – Chap. 4 ... 41 © A. Khouas, 2008 4. Exemples de codage Réf. : Microprocesseur, support de cours Dr. J. Y. Haggège Architecture – Chap. 4 42 © A. Khouas, 2008 5. Conclusion Ce qui est important à retenir : Architecture – Chap. 4 Architecture interne du 8086 Représentation et codage des instructions Exécution des instructions Jeux d’instruction du 8086 43 © A. Khouas, 2008