Télécharger le rapport (Word)

Option Informatique Industrielle ESSI - 19 Avril 2002

ESSI - 19 Avril 2002 ESSI - 19 Avril 2002

Baudot Romaric

Joulié Gabriel

Rampal Vincent

2

INTRODUCTION ................................................................................................................................................. 3

PRESENTATION DU LECTEUR DE CARTE ................................................................................................. 3

CONSIDERATIONS MATERIELLES ......................................................................................................................... 3

CODAGE DES DONNEES SUR UNE CARTE .............................................................................................................. 3

REALISATION DU COMPOSANT PRINCIPAL ............................................................................................ 4

INTRODUCTION ................................................................................................................................................... 4

SCHEMA DE PRINCIPE .......................................................................................................................................... 5

LES DIFFERENTS MODULES .................................................................................................................................. 5

SCHEMA LOGIQUE ............................................................................................................................................... 5

CABLAGE COTE COMPOSANT ............................................................................................................................... 7

COTE 68020 ......................................................................................................................................................... 8

PARTIE LOGICIEL ............................................................................................................................................ 9

INTRODUCTION ................................................................................................................................................... 9

LISTING DU PROGRAMME .................................................................................................................................... 9

CONCLUSION ..................................................................................................................................................... 9

3

Introduction

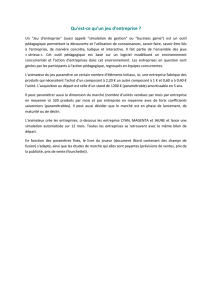

Pour aborder les problèmes d’informatique industrielle, il nous à été demandé de réaliser

un composant ayant pour but le décodage d’informations contenues sur une carte magnétique.

Le principe est de créer une carte sur laquelle est greffé un lecteur de carte magnétique, une

puce programmable servant de décodeur de données ainsi que de module de communication

avec un processeur 68020. De plus, il est nécessaire de développer le programme s’exécutant

sur le processeur 68020 et permettant d’afficher les données lues sur la carte magnétique.

Lors d’une année précédente, un étudiant de l’ESSI a développé une carte mère

supportant un microprocesseur 68020. Il nous a été demandé de développer notre carte de

décodage pour qu’elle soit compatible avec la carte mère ESSI et ainsi pouvoir travailler avec

du matériel fait maison.

Présentation du lecteur de carte

Considérations matérielles

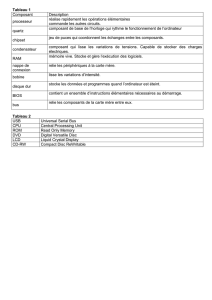

Boîtier externe relié par 5 fils :

présence carte (fil jaune) actif à l’état haut

données en logique inverse (fil vert)

horloge (fil bleu), n’est valide qu’après que les données soient passées à 0

alimentation (fil rouge) +5V

masse (fil noir)

Codage des données sur une carte

Sur la carte, les données sont codées sur plusieurs pistes qui comportent chacune une

information différente. Nous ne nous intéresserons qu’à deux d’entre elles, à savoir l’horloge,

une suite de 0 et 1 visant à rythmer le passage de la carte pour en permettre le décodage, et

une piste de données comprenant notamment un nom et un numéro.

Lors du passage d’une carte, on reçoit les bits en série avec d’abord le bit de poids le

plus fort et le bit de parité en dernier. Les données sont codées suivant un dérivé de l’ASCI. Il

faut faire attention car les données sont codées en logique inverse sur la carte magnétique,

ainsi l’information reçue est le complémentaire de l’information affichée. De plus l’ASCI est

sur 7 bits (0x00 - 0x7F) mais on utilisa uniquement des lettres minuscules et des nombres (pas

de caractères spéciaux, ni majuscules…). Ces caractères sont codés au format 11X XXXX

pour les lettres car elles vont de 0x61 à 0x7A, et au format 011 XXXX pour les chiffres qui

vont de 0x30 à 0x39. Ainsi, on fera l’économie du codage et donc de la transmission du 6ème

bit, puisqu’il est toujours à 1. Le 7ème bit correspond à la parité des 6 précédents, il sera

transmit, mais ne sera pas traité dans cette application. On se contentera de reformer l’octet et

de le transmettre à la carte mère. Cet octet aura tout de même une différence par rapport à de

l’ASCI : le bit de poids fort codera la présence de la carte.

4

Réalisation du composant principal

Introduction

La fonction de ce composant et de décoder les informations en provenance du lecteur de

carte magnétique et de les transmettre au processeur 68020 via le bus de données, quand

celui-ci l’interroge. Ce composant sera donc placé entre le lecteur de carte et le processeur

68020. Ce composant devra donc traiter les signaux en provenances du lecteur de carte, mais

aussi ceux du bus d’adresse, permettant de sélectionner, ainsi que ceux du bus de données. Le

composant doit aussi gérer les signaux de contrôles ASTROBE, indiquant que l’adresse

présente sur le bus d’adresse est correcte, DSAC0, indiquant que 8 bits de données sont

présentes sur le bus de données et TZL indiquant que les données présentent sur le bus de

données sont correctes.

En regardant les spécifications de la carte mère faite à l’ESSI, on s’aperçoit, que la plage

d’adresse allouée pour la carte est comprise entre $00800000 et $00FFFFFF. Comme une

seule carte va être connectée, nous avons décidé de simplifier le décodeur d’adresse. Ainsi la

carte sera sélectionnée si les 8 bits de poids forts sont à 0 et le bit numéro 23 à 1 sur le bus

d’adresse.

Pour créer ce composant, nous allons utiliser un FPGA, que nous allons programmer.

L’ESSI nous à donc mis à disposition un composant Altera et son interface de programmation

MAX+PLUS II.

1

0

0

1

0

1

0

Data

Horloge

Présence

Carte

Données lues

5

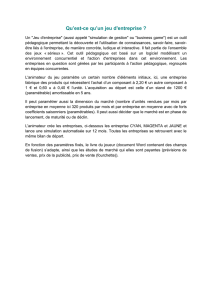

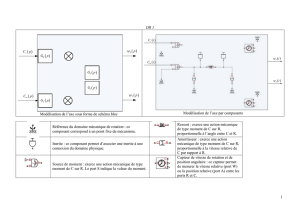

Schéma de principe

Lecteur de cartes

Bus de donnée

Bus d’adresse ASTROBE

DSAC

0

TZL

Comparateur

à 8

Registre à

décalages

Décodeur

d’adresse

Compteur

modulo 8

Validation

Lecteur de cartes

Bus de donnée

Bus d’adresse ASTROBE

DSAC

0

TZL

Comparateur

à 7

Registre à

décalages

Décodeur

d’adresse

Compteur

modulo 7

Validation

Les différents modules

Le registre à décalage, sert à construire l’octet pour le µP. Le bit de parité sera stocké

mais jamais transmit.

Le compteur modulo 7 permet de savoir combien de bits ont été lus.

Les deux modules précédents utilisent le signal d’horloge du lecteur de carte. Il est

nécessaire d’inhiber ce signal tant que data n’est pas passé une fois à zéro.

Le comparateur a sept envoie un signal quand la lecture d’un octet est terminée.

Le décodeur d’adresse envoie un signal type Chip Select pour dire quand le composant

est adressé.

La partie validation met les signaux DSAC0 et TZL à 0 si :

Soit le composant est sélectionné et la carte n’est pas présente.

Soit le composant est sélectionné et 7 bits ont été lus sur la carte magnétique et qu’ils

n’ont pas encore été transmis sur le bus de données.

Schéma logique

[ Voir page suivante ]

6

6

7

7

8

8

9

9

1

/

9

100%