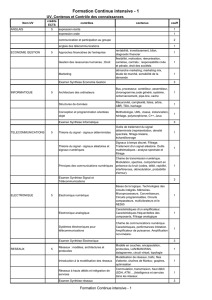

Électronique Numérique : Cours BTS MSI - Systèmes et Logique

Telechargé par

Bertrand Tueno Yangwa

1

ELECTRONIQUE NUMERIQUE 1BTS MSI BERTRAND TUENO

1. Systèmes de numération et codes

2. Système de numération

3. Conversion

4. Ecriture des nombres signés

5. Codes

6. Arithmétique binaire

7. Addition

8. Soustraction

9. Multiplication

10. Division

11. Représentation des nombres signés

12. Opération sur les nombres signés

13. Addition en DCB

14. Portes logiques et algèbre de Boole

15. Définitions

16. Table de vérité

17. Portes logiques

18. Algèbre de Boole

19. Mise sous forme algébrique des circuits logiques

20. Simplification des fonctions logiques

21. Généralités

22. Méthodes de simplification des fonctions logiques

23. Circuits combinatoires

24. Additionneur binaire

25. Soustracteur binaire

26. Comparateur

27. Codeur

28. Décodeur

29. Multiplexeur

30. Démultiplexeur

Les lecons 1 à 12 ont été abordees dans le volume 1(informatique generale)

2

ELECTRONIQUE NUMERIQUE 1BTS MSI BERTRAND TUENO

13. Addition en DCB

14. Portes logiques et algèbre de Boole

L'ordinateur est un dispositif électronique sophistiqué qui traite l'information mise sous forme

d'impulsions électriques traduisant les chaînes binaires utilisées pour représenter les symboles

qu’on y introduit codés sous forme d’une suite bits. Rappelons qu’un ordinateur ne comprend que

les impulsions électriques.

Les traitements, pour leur part, sont essentiellement réalisés à l'aide d'opérations telles l'addition,

la soustraction, la multiplication, la division, la comparaison. Plus fondamentalement, les

opérations sont composées d'opérations logiques qui sont effectuées par des circuits logiques de

base appelés portes. Une porte est en fait un circuit combinatoire à une ou plusieurs entrées et à

au moins une sortie. Les conditions aux entrées d'une porte déterminent l'état des sorties. Il existe

trois portes de base correspondant aux trois opérations logiques: OU, ET, NON.

Algèbre de Boole .

On dit que les portes OU, ET, NON sont des opérateurs booléens, parce qu'ils impliquent ou

traitent des variables booléennes, c'est à dire des variables logiques qui ne peuvent prendre que

deux valeurs: 0 et 1. Le terme booléen vient du nom du mathématicien anglais George Boole

(1815-1864), qui fit une analyse mathématique de la logique.

L'ensemble des règles relatives au traitement des variables booléennes est appelé algèbre de

Boole ou treillis booléen.

Nous reviendrons plus loin aux règles du treillis booléen. Mais d'abord, regardons de plus près les

trois portes fondamentales: OU, ET, NON.

La porte OU .

3

ELECTRONIQUE NUMERIQUE 1BTS MSI BERTRAND TUENO

L'opération OU appliquée à une ou plusieurs variables conduit à l'addition logique de ces

variables (résumée dans la table de vérité qui suit). Elle est aussi appelée réunion et elle est notée

par le signe , ou plus simplement par +.

4

ELECTRONIQUE NUMERIQUE 1BTS MSI BERTRAND TUENO

Figure 1 : Porte OU. Table de vérité

TABLE DE VÉRITÉ

L'addition logique peut s'étendre aux chaînes binaires où les bits de même rang sont additionnés

selon la table de vérité de l'addition simple:

Figure 2 : Porte Ou, Table binaire

Pour représenter la porte OU dans les circuits, on utilise le symbole suivant:

Figure 3 : Porte OU, Symbole

a

b

a + b ( a U b )

Bien sûr, la boîte noire qui porte le nom OU dans le schéma ne décrit pas le circuit électronique

approprié pour réaliser la fonction OU. Voici un circuit électrique simple qui pourrait réaliser la

fonction OU:

a U b

entrées

sortie

a

b

a+b

0

0

0

0

1

1

1

0

1

1

1

1

+ 0 1

0 0 1

1 1 1

OU

0 1 0 1

0 1 1 1

0 0 1 1

5

ELECTRONIQUE NUMERIQUE 1BTS MSI BERTRAND TUENO

Figure 4 : Porte OU, Schéma

Un signal électrique à l'entrée actionne un aimant provoquant la fermeture de la porte et

permettant le passage du courant. Disons tout de suite, qu'un tel circuit est tout à fait démodé. Sa

grande simplicité nous permet cependant de bien comprendre ce que fait le circuit. Nous

aborderons plus loin les technologies de maintenant.

La porte ET .

Un circuit ET possède, tout comme le OU, deux ou plusieurs entrées et une sortie. Le ET

correspond au produit logique ( ) ou X ou encore a l’intersection

Figure 5 : Porte ET, Table de vérité

TABLE DE VÉRITÉ

L'opération de multiplication peut comme les précédentes s'étendre aux chaînes binaires.

a b

entrées

sortie

a

b

a .b

0

0

0

0

1

0

1

0

0

1

1

1

aimant

courant

entrée

sortie

OU

entrée

0 1

0 0 0

1 0 1

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

1

/

57

100%